-

单光子探测在激光雷达三维成像[1]、荧光寿命成像[2-3]、激光通信[4]等领域具有广泛的应用前景。基于盖革雪崩光电二极管(Avalanche Photodiode, APD)的单光子焦平面探测器具有灵敏度高、探测距离远、测距精度高等特点[5-8],它通过计量光子飞行时间实现距离探测,光子飞行时间由探测器内的读出电路(Readout Integrated Circuit, ROIC)记录、存储和输出,读出电路内的时间-数字转换模块负责将时间信息转换为数字码值,计时精度决定整个探测系统的测距精度,是ROIC内的关键模块。

在M×N规模的焦平面探测器内,若各像元具备独立计时能力,需M×N个计时单元,TDC设计面临面积和功耗的挑战。TDC有多种实现方案:基于单一计时器型的TDC结构简单、静态功耗低,但计时精度受限于参考时钟频率,难以实现高精度;基于游标型的TDC能够实现超高精度,但功耗高、版图面积大,无法应用于小像元中心距阵列。

针对中大规模焦平面的应用特点,一些研究机构采用复合型的TDC结构,将TDC分为粗计时和细计时两个段位,这种结构可以兼顾精度、功耗和版图面积[9-10]。如何选择不同的分段组合、各分段如何选择底层的TDC结构和优化设计对整个TDC的性能有着重要影响,是值得研究的重要方向。此外,由于TDC的不同段之间存在时钟信号失配,计数码值的存储和转换会存在误码现象,严重影响时间数字转换的准确性。因此,有必要针对多段式TDC的误码进行分析并研究解决方案,在低功耗条件下实现高计时精度和大时间量程。

文中报道了一款适用于64×64规模InGaAs盖革APD面阵的时间数字转换电路。该面阵TDC针对无扫描航空激光雷达三维测距时间分辨率高、计时量程大、探测区间内每一个像素可检测回波光子和记录光子飞行时间的应用需求,采用高、中、低三段式TDC结构和延迟采样方案,实现高时间分辨和低误码计时。对高、中、低段位计时原理、电路结构、延迟采样方案进行了分析。流片和测试结果表明时间分辨率可达0.5 ns,20 kHz帧频功耗380.5 mW。

-

基于盖革APD焦平面的三维激光雷达工作原理如图1所示,通过测量光子飞行时间计算被测目标与探测器间的距离。探测系统脉冲激光源发射光子,焦平面内的读出电路开始计时,光子到达目标点后反射,回波信号触发APD雪崩,探测器感应到雪崩电流并触发读出电路停止计时。

光子飞行时间由读出电路的时间数字转换模块记录并存储。根据不同的共享方式,时钟驱动型阵列TDC主要分为像素独享型、全局共享型、局部共享型三种方案。像素独享型方案基于门控环振(Gated Ring Oscillator, GRO)[2],像素内部集成独立门控环振,像素时间量化独立、无全局时钟线、像素间高频干扰小,但是GRO受PVT影响,随阵列规模增大,存在各像素计时不均匀问题。全局共享型方案共用一个外置型TDC,该方案结构简单,可通过提高量化时钟频率提升时间分辨率。但是随着像素规模增加,要实现大量程需多条全局时钟线,时钟网络布局复杂,多路信号间相互干扰严重、各路时钟延迟难以匹配,在阵列应用中难以兼顾量程、计时精度。

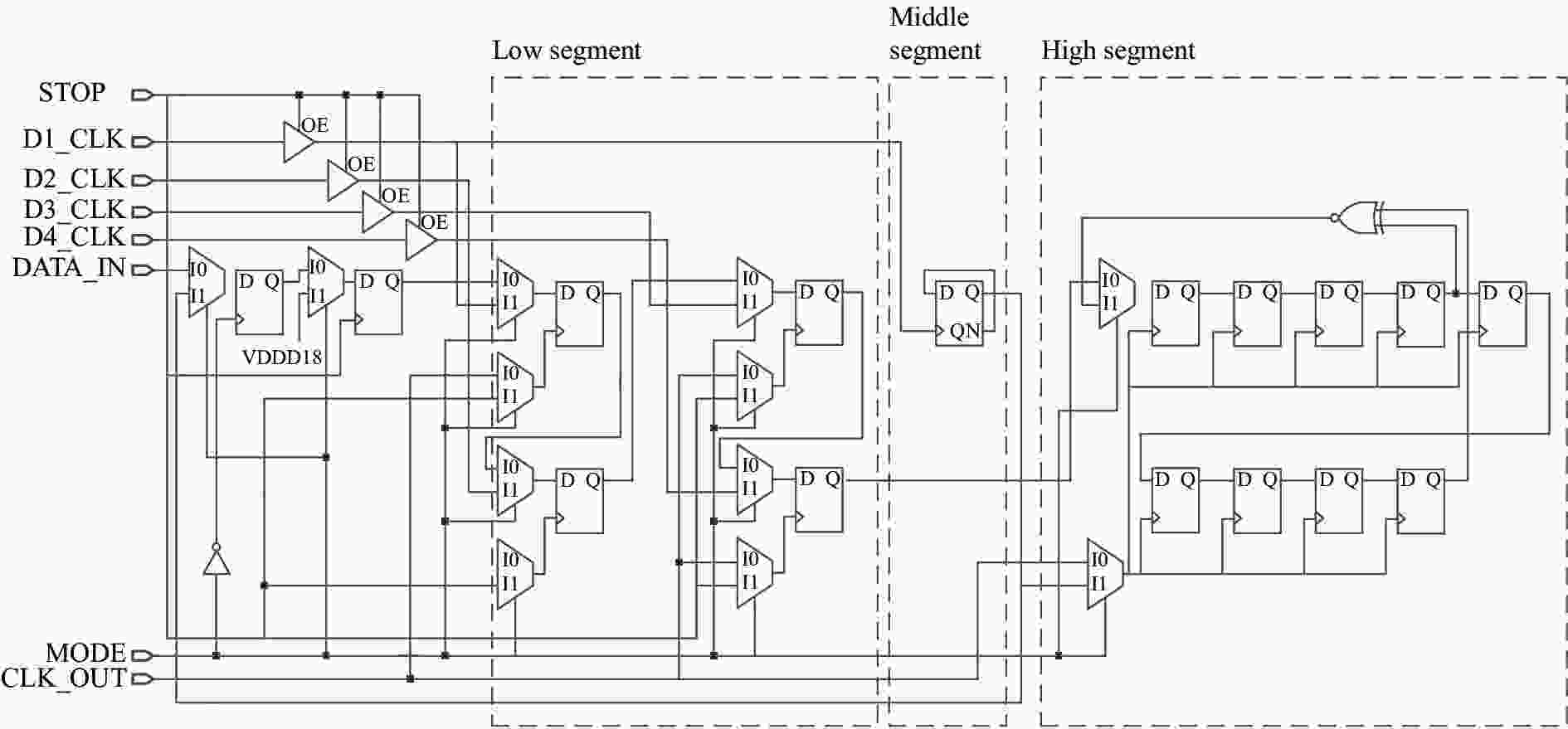

局部共享型三段式TDC的结构如图2所示。低段位TDC基于延迟锁相环(Delay Locked Loop, DLL),环路为单极点稳定系统且具有低抖动、低相位噪声优点[11],该模块内部的压控延迟链生成的多路分相时钟可突破时钟周期限制,实现高精度计时。中高段位TDC位于像素内部,降低单像素功耗对于降低全局电路的功耗具有重要意义,在低段位与高段位之间插入分频计数器作为中段位TDC,分频后的信号作为高段位TDC的时钟信号,进而降低像素内时钟频率。高段位采用线性反馈移位寄存器,该模块为同步电路,具有结构简单、功耗低、时钟信号同步的优势。时间转换完成后,结果存储在每个像素的寄存器块内,在读出模式下被配置为移位寄存器并通过选择信号逐步开启每个像素,各像素数据通过总线输出。这种面阵TDC方案可满足无扫描激光雷达每个探测窗口内,所有像素都可记录光子飞行时间的应用需求且兼顾高时间分辨率和计时量程。

TDC的工作方式如图3所示,基于参考时钟的上升沿,待测时间分为三个部分,时间转换结果可表示为:

$$ {\Delta T}_{\rm TEST}={\Delta T}_{\rm START}+N{T}_{\rm CLK}-{\Delta T}_{\rm STOP} $$ (1) 式中:NTCLK表示停止计时后计数器的结果;ΔTSTART和ΔTSTOP为经过低段位TDC量化后的时间值。

-

三段式TDC各段位采用不同的结构方案,其结构如图4所示。各段位采用不同的技术方案,段位之间可能会因失配造成进位误码,同时具备高计时精度和低误码率是设计重点。在门控时钟模式下,高速参考时钟仅在计时模式下进入TDC模块内部,非计时模式屏蔽高频参考时钟,其功耗仅由漏电流和门控模块之前时钟路径上的动态功耗组成,有效降低电路平均功耗。通过时钟选择器,读出模式下低速时钟进入像素内部,不同工作模式的时钟彼此之间相互独立。在这种工作方式下,数字码值无法并行输出,片内无法进行数据转换,但是在时间数字转换过程中,输出缓冲器不需驱动大容值片外负载,可将影响TDC转换精度的开关噪声降至最低且不需要专用的读出寄存器,降低硬件资源开销。

-

如图5所示,DLL由启动模块、鉴相器(Phase Detector, PD)、电荷泵(Charge Pump, CP)、压控延迟链、环路滤波器(Loop Pass Filter, LPF)等模块组成,VCDL是实现高时间分辨率的关键,通过插值技术提取分相时钟信号可突破参考时钟周期限制。假设VCDL的级数为N,参考时钟频率为

${T}_{\rm ref}$ ,TDC可实现的时间分辨率为:$$ {T}_{LSB}=\frac{{T}_{{\rm{ref}}}}{N} $$ (2) 为在250 MHz参考时钟频率下实现0.5 ns时间分辨率,VCDL设计为8级,如图6所示,延迟单元为差分电路,与单端结构相比,差分结构能够更好地抑制共模干扰,降低共模噪声对电路的影响。NMOS管M1和M2为信号输入管,M3、M5由VCTRL信号控制,当VCTRL控制电压大小改变,压控管的充放电能力随之改变,延迟时间改变,其随着控制电压的增加而增加。

由图5和图7可知,在锁定状态下,CLKREF与D8_CLK的相位相差2π,相邻时钟信号的相位差为π/4,利用时钟内插法提取8级压控延迟链的4路相邻时钟作为分相时钟信号,在TDC停止信号到来时刻,锁存器锁存分相时钟的当前值。4路相邻分相时钟以格雷码形式变换,相邻状态下只有1 bit信号翻转,格雷码转换方式能够避免因多路电平同时翻转出现高瞬态功耗的情况。

如图8所示,多级分相时钟信号和TDC开启计时信号通过H型时钟网络进入各像素单元,全局信号能够等延迟进入各像素单元,有效提升像素计时一致性。

-

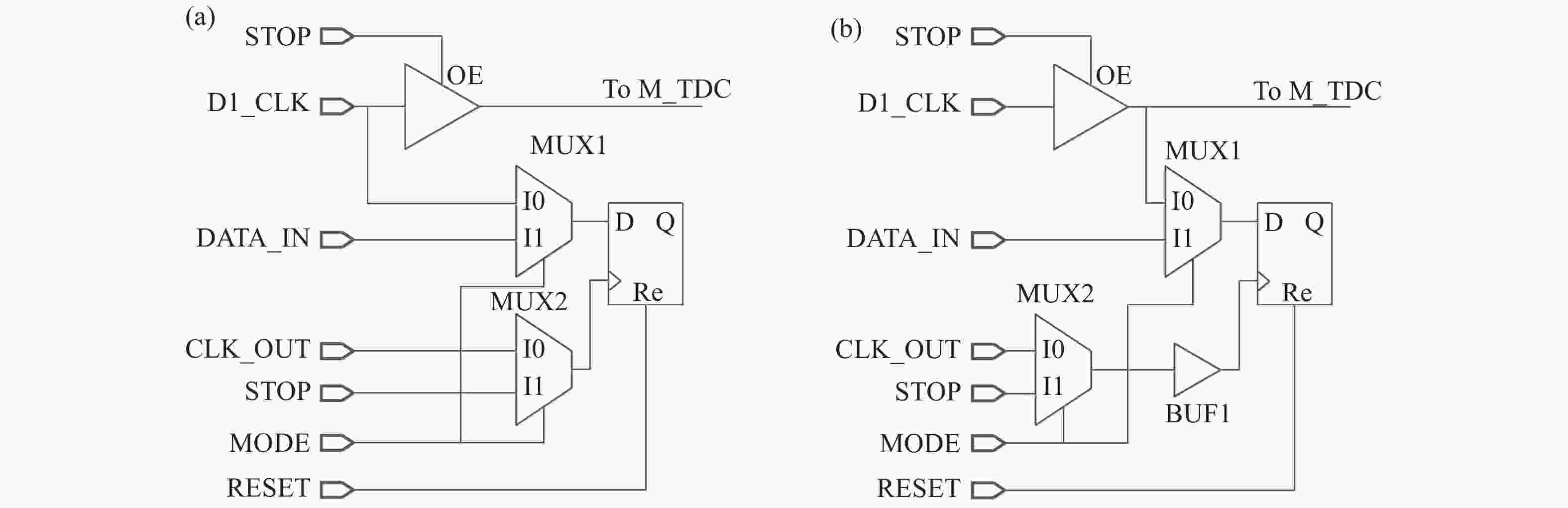

低段位数据锁存电路如图9所示,D1_CLK信号既是低段位信号,又是中段位输入时钟,当STOP信号在D1_CLK上升沿附近到来,该上升沿能够正常驱动中高段位计数器,但是受限于低段位锁存器的信号建立时间,该信号有锁存错误的风险,引发进位误码,导致TDC的非线性性能恶化。如图10所示,假设STOP信号在不同的区域到来,不同区域TDC转换结果如表1所示,当STOP信号在区域B或区域D到来,会出现锁存误码。

图 9 低段位数据锁存电路。 (a)原有数据锁存电路; (b)改进数据锁存电路

Figure 9. Low segment data latch circuit. (a) Data latch circuit before optimization; (b) Data latch circuit after optimization

如图9(a)所示的原方案,D1_CLK信号经过传输门后将继续传输到中段位,低段位的锁存器直接锁存D1_CLK值,中高段位TDC为时钟沿触发型计数器,识别传输门的稳定输出信号,低段位锁存器锁存快速变换的时钟信号,不同节点处寄生电容值不同,传输延迟失配极易造成段间进位误码。优化后数据锁存电路如图9(b)所示,低段位TDC锁存经传输门输出的信号,实现中高段位和低段位间的时钟延迟匹配并在MUX2和锁存器之间插入传输延迟略大于传输门延迟的缓冲器BUF1,待D1_CLK信号稳定后再采样,通过延迟采样的方式降低误码率。

表 1 时间数字转换电路计数值

Table 1. Count value of time-to-digital converter circuit

STOP signal effective area A B C D E Middle and high TDC count value n n+1 n+1 n+1 n+1 D1_CLK latch level 0 0 1 1 0 Latched correctly ? No Yes No Yes No 中段位TDC采用异步计数器结构,在面阵应用中,中高段位TDC每个像素单元独有,降低单像素功耗对于降低电路整体有显著意义,每级异步计数器可将输入时钟频率降低1/2,但是每级异步结构会引入延迟误差,级数越多,引入的延迟误差越大,会造成更大的段间失配,因此中段位TDC选用单级异步计数器。

高频时钟经中段位分频后,作为高段位的时钟信号,STOP信号到来后,锁存器记录分频器的输出值,但是由于分频器的输出相对于输入信号存在一定延迟,如果STOP信号在图11的区域A或者区域B到来会导致段间误码。

通过改进电路逻辑,中段位TDC的锁存电路如图12所示。MODE=1时,TDC处于计时模式; MODE=0时,TDC处于读出模式。STOP信号到来后,中段位TDC停止工作,但是其输出不会马上进入锁存器,START信号下降沿锁存中段位转换码值,此时中段位信号已经稳定,不会造成锁存误码。

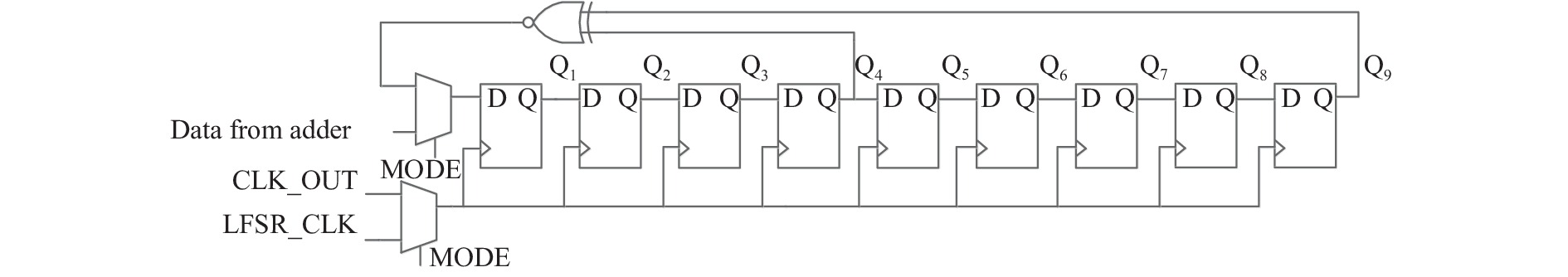

如图13所示,高段位TDC为9 Bbits线性反馈异或门反馈型移位寄存器,根据公式(3)的码值变化关系,可实现(2n−1)个状态的循环。移位寄存器为同步结构,各级之间具有良好的时间一致性,其驱动时钟为中段位分频后的时钟信号,在低速条件下,移位寄存器能够稳定工作。

$$ \begin{split} \\ {{\rm{Q}}}_{1}=\overline{{{\rm{Q}}}_{4}+{{\rm{Q}}}_{9}},{{\rm{Q}}}_{2}={{\rm{Q}}}_{1},{{\rm{Q}}}_{3}={{\rm{Q}}}_{2},{{\rm{Q}}}_{4}={{\rm{Q}}}_{3}\\ {{\rm{Q}}}_{5}={{\rm{Q}}}_{4},{{\rm{Q}}}_{6}={{\rm{Q}}}_{5},{{\rm{Q}}}_{7}={{\rm{Q}}}_{6},{{\rm{Q}}}_{8}={{\rm{Q}}}_{7},{{\rm{Q}}}_{9}={{\rm{Q}}}_{8} \end{split}$$ (3) 与中低段位相比,高段位TDC不需增加额外的锁存器,当STOP信号到来后其停止工作,数据稳定存储在各级节点且因为其自身为移位结构,在读出模式下可与中低段位数据锁存器重新配置为移位寄存器,通过总线将数据输出,可实现计时、数据存储一体化,有效降低电路的硬件开销,优化版图面积。

-

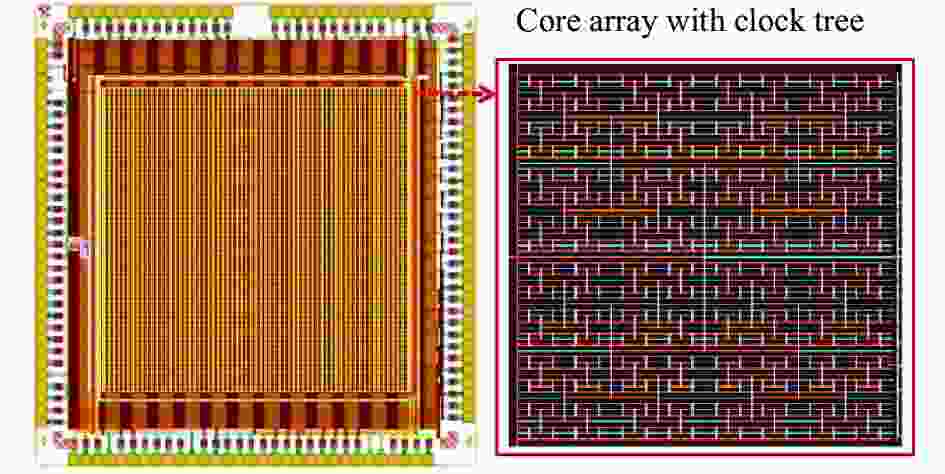

该电路采用0.18 µm标准CMOS工艺流片,包括时序控制模块、输出模块、键压PAD,64×64面阵型TDC总面积为9.1 mm × 9.1 mm,电路键压金线后的显微镜照片如图14所示。

-

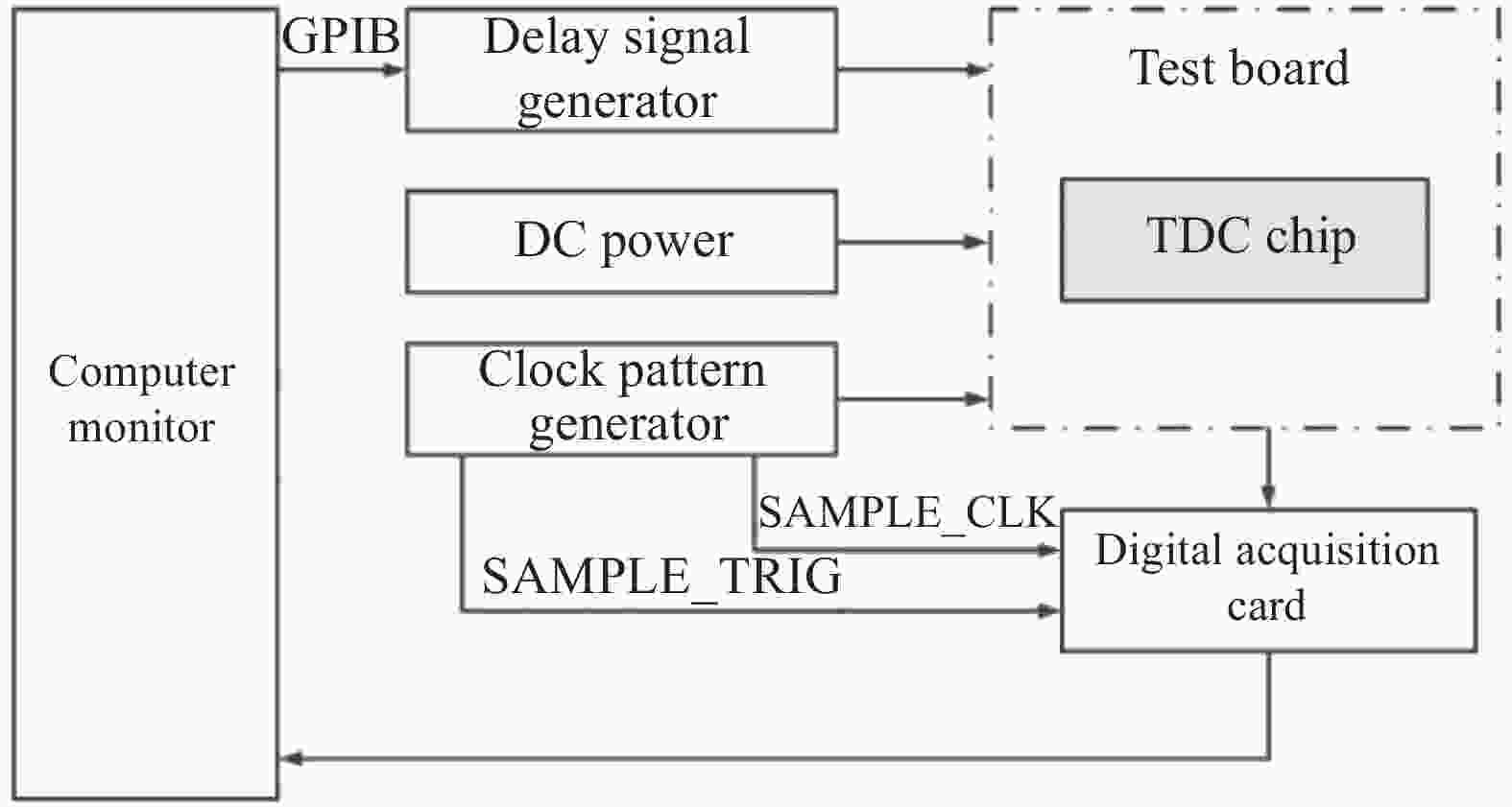

TDC测试系统框图如图15所示,为验证TDC的全段位转换性能,STOP信号以0.1 ns间隔步进,从0~4087.5 ns测试40875个数据点,验证TDC的转换性能,全量程范围内转换曲线如图16(a)所示。

图 16 时间数字转换曲线。 (a)全量程转换曲线; (b) 1112 ns局部转换曲线

Figure 16. Time-to-digital conversion curve. (a) Full-scale conversion curve; (b) 1112 ns partial amplification conversion curve

对测试结果进一步分析,将1112 ns处的转换特性放大,其转换特性如图16(b)所示,该曲线反映了1112~1116 ns的时间转换特性,将整个量程范围内的转换特性切换成与参考时钟周期相同的时间片,由表2的统计结果可知,各个周期内的转换步长规律大部分与图16(b)所示曲线符合,即呈现固定的规律性分布。

表 2 时间数字转换电路转换步长统计规律

Table 2. Conversion step size statistics of time-to-digital converter circuit

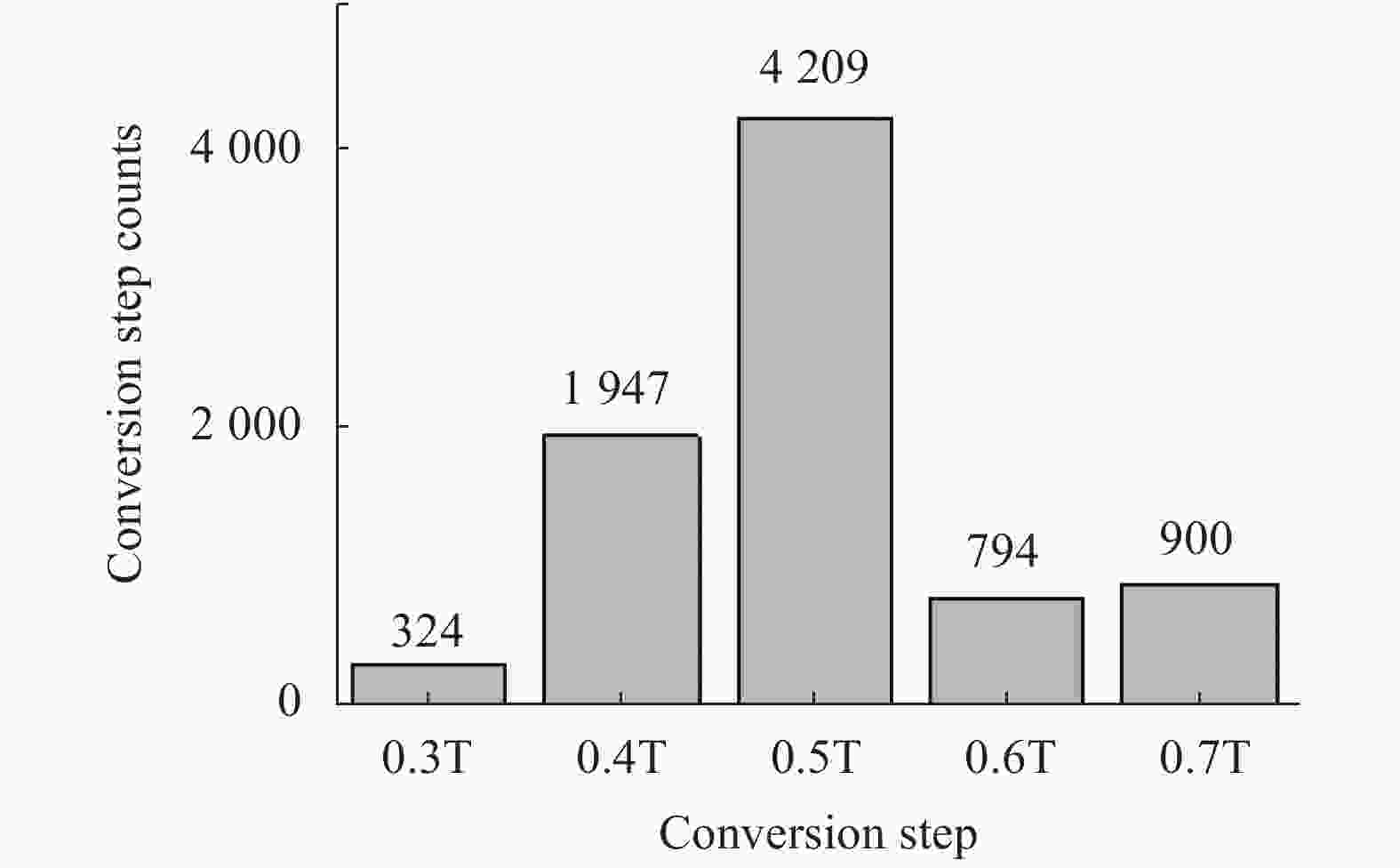

Ideal conversion step Actual conversion step 0-0.5T 0.7T 0.5-1.0T 0.4T 1.0-1.5T 0.5T 1.5-2.0T 0.5T 2.0-2.5T 0.4T/0.3T 2.5-3.0T 0.5T 3.0-3.5T 0.5T 3.5-4.0T 0.5T/0.6T 对全量程转换步长进行统计,统计结果如图17所示,计算平均值后,其等效时间分辨率为0.5T, TDC存在固定误差,该误差不会导致TDC的功能出现异常,但是会造成DNL、INL性能下降。

若分相时钟具有理想的相位差,DLL参考时钟经过压控延迟链后能够输出等间隔为0.5 ns的时钟信号,但是因为各级延迟单元之间可能存在工艺偏差、分相时钟进入TDC的各路径,负载电容存在偏差,TDC接收到的各分向时钟之间的相位差不是理想的π/4。

DLL的分相时钟输出信号为差分信号,需要转换为单端信号后进入TDC,DLL的差分转单端电路,转换后的信号占空比低于50%,且低段位TDC的4路信号,D1_CLK信号作为后级计数器的时钟需要驱动后级电路,其负载电容稍大于D2_CLK、D3_CLK、D4_CLK处的负载电容,故D1_CLK信号的延迟时间可能稍大于其3路时钟。

-

对TDC的非线性性能进行测试,结果如图18和图19所示,可得−0.4 LSB≤ DNL≤ 0.4 LSB,−0.4 LSB ≤ INL ≤ 0.6 LSB,DNL<1LSB,表明TDC传输特性保持单调性,数据转换误码概率较低。

引起DNL和INL的原因包括以下几点:(1) 时钟抖动,四相位时钟由DLL提供,DLL的分相时钟存在时钟抖动;(2) DLL的分相时钟为差分信号,各路信号需转换为单端信号后经过缓冲器再进入TDC,该电路的差分转单端电路没有实现50%占空比校正且缓冲器的上升、下降时间不一致,如图20所示,会进一步导致占空比偏离50%,进入TDC的不是占空比50%的理想分相时钟。

根据表3,在类似工艺条件下,所设计的面阵型TDC能够实现亚纳秒时间分辨率且具备较高的计时量程,在64×64面阵规模下功耗没有显著上升,后续可通过优化分相时钟性能增加参考时钟频率、优化像素电路,进一步提升电路性能。

表 3 时间数字电路指标总结

Table 3. Summary of time-to-digital circuit index

Parameter Ref. [2] Ref. [12] Ref. [13] This work CMOS technology/nm 350 130 350 180 Supply voltage/V 3.3 1.2 3.3 1.8 Pixel pitch/μm 150 50 100 100 Pixel array 32×32 32×32 16×16 64×64 TDC frame rate/kHz 100 500 20 20 TDC resolution/ns 0.312 0.119 0.575 0.5 DNL/LSB 0.06 0.4 −0.57–0.58 −0.4–0.4 INL/LSB 0.22 1.2 −0.9–0.57 −0.4–0.6 TDC range/μs 0.32 0.1 2 4.08 Power consumption/mW 315 90/Core only 151.8 380.5 -

设计了一款应用于100 μm中心距、64×64规模盖革雪崩焦平面阵列的时间数字转换电路,13 bit三段式TDC采用局部共享方案,低段位全局共享,中高段位像素独享,250 MHz参考时钟下可实现0.5 ns时间分辨率,典型工作频率下,DNL–0.4~0.4 LSB,INL–0.4~0.6 LSB,延迟采样电路能够有效降低锁存误码概率,提升TDC的非线性性能。测试结果与仿真结果吻合,达到预期目标。可以进一步推广用于中等规模单光子探测用盖革雪崩焦平面的读出电路,实现高精度和低误码计时。

Pixel-level high resolution and low error rate time-to-digital converter circuit of single photon detection InGaAs avalanche focal plane array

-

摘要: 单光子探测在量子信息、生物医学、激光雷达成像等领域具有重要应用前景,InGaAs盖革雪崩焦平面具有单光子探测灵敏度,通过计量光子飞行时间实现距离探测,时间数字转换精度决定整个探测系统的测距精度,是近年来单光子探测领域的研究热点。设计了一款64×64面阵型像素级高分辨低误码时间数字转换阵列电路(Time to Digital Converter, TDC),采用局部共享型高中低三段式异步周期TDC结构。低段位TDC全阵列共享,基于压控延迟链(Voltage Control Delay Line, VCDL)分相时钟实现亚纳秒计时;中高段位每个像素独享,中段位采用分频计数器降低时钟频率,降低阵列整体功耗,高段位采用线性反馈移位寄存器实扩展计时量程并实现计时、数据存储、输出一体化。采用延迟采样方案显著降低了因段间计数时钟不匹配导致的数据锁存误码问题。采用0.18 µm CMOS工艺流片,实测250 MHz参考时钟频率下分辨率0.5 ns,积分非线性−0.4~0.6 LSB,微分非线性−0.4~0.4 LSB,TDC转换单调,有效量程位数13位,20 kHz帧频功耗380.5 mW。Abstract: Single-photon detection has important application prospects in quantum information, biomedicine and laser radar 3D imaging. InGaAs Geiger avalanche focal plane has single-photon sensitivity. Distance detection is achieved by measuring time of photon flight. Time-to-digital conversion accuracy determines the ranging accuracy of the detection system and this direction is the focus of single photon detection in recent years. A high resolution and low error rate 64×64 array type pixel level time-to-digital converter (TDC) circuit adopting three-stage asynchronous periodic counter structure was designed for InGaAs Geiger-mode avalanche focal plane array applications. Sub-nanosecond time resolution was realized by a voltage-controlled delay chain as well as a fine TDC that was shared by the entire array. The pixel level middle and coarse TDC used a divider counter to reduce the clock frequency and a linear feedback shift register to achieve a large time range, respectively. The high-segment coarse TDC can achieve timing, data storage and output integration through the register chain. The data conversion error rate originating from the mismatch of counting clocks between different stages was significantly reduced by incorporating of a delayed sampling scheme. A timing resolution of 0.5 ns at a reference clock frequency of 250 MHz, an integral nonlinearity of −0.4 to 0.6 LSB, a differential nonlinearity of −0.4 to 0.4 LSB, an effective digit of 13 bits, and a power consumption of 380.5 mW at 20 kHz frame rate are attained based on a 0.18 µm digital-analog hybrid CMOS technology. The TDC remains monotonous within the conversion range.

-

表 1 时间数字转换电路计数值

Table 1. Count value of time-to-digital converter circuit

STOP signal effective area A B C D E Middle and high TDC count value n n+1 n+1 n+1 n+1 D1_CLK latch level 0 0 1 1 0 Latched correctly ? No Yes No Yes No 表 2 时间数字转换电路转换步长统计规律

Table 2. Conversion step size statistics of time-to-digital converter circuit

Ideal conversion step Actual conversion step 0-0.5T 0.7T 0.5-1.0T 0.4T 1.0-1.5T 0.5T 1.5-2.0T 0.5T 2.0-2.5T 0.4T/0.3T 2.5-3.0T 0.5T 3.0-3.5T 0.5T 3.5-4.0T 0.5T/0.6T 表 3 时间数字电路指标总结

Table 3. Summary of time-to-digital circuit index

Parameter Ref. [2] Ref. [12] Ref. [13] This work CMOS technology/nm 350 130 350 180 Supply voltage/V 3.3 1.2 3.3 1.8 Pixel pitch/μm 150 50 100 100 Pixel array 32×32 32×32 16×16 64×64 TDC frame rate/kHz 100 500 20 20 TDC resolution/ns 0.312 0.119 0.575 0.5 DNL/LSB 0.06 0.4 −0.57–0.58 −0.4–0.4 INL/LSB 0.22 1.2 −0.9–0.57 −0.4–0.6 TDC range/μs 0.32 0.1 2 4.08 Power consumption/mW 315 90/Core only 151.8 380.5 -

[1] Niclass C, Soga M, Matsubara H, et al. A 100-m range 10-frame/s 340×96-pixel time-of-flight depth sensor in 0.18 µm CMOS [J]. IEEE Journal of Solid State Circuits, 2013, 48(2): 559-572. doi: 10.1109/JSSC.2012.2227607 [2] Villa F, Lussana R, Bronzi D, et al. CMOS imager with 1024 SPADs and TDCs for single-photon timing and 3-D time-of-flight [J]. IEEE Journal of Selected Topics in Quantum Electronics, 2014, 20(6): 364-372. doi: 10.1109/JSTQE.2014.2342197 [3] Rocca F M D, Mai H, Hutchings S W, et al. A 128×128 SPAD motion-triggered time-of-flight image sensor with in-pixel histogram and column-parallel vision processor [J]. IEEE Journal of Solid State Circuits, 2020, 55(7): 1762-1775. doi: 10.1109/JSSC.2020.2993722 [4] Aull B F, Duerr E K, Frechette J P, et al. Large-format Geiger-mode avalanche photodiode arrays and readout circuits [J]. IEEE Journal of Selected Topics in Quantum Electronics, 2018, 24(2): 1-10. [5] Jiang X, Itzler M, Donnell K O, et al. InP-based single-photon detectors and Geiger-mode APD arrays for quantum communications applications [J]. IEEE Journal of Selected Topics in Quantum Electronics, 2015, 21(3): 5-16. doi: 10.1109/JSTQE.2014.2358685 [6] Aull B F, Reich R K, Ward C M, et al. Detection statistics in Geiger-mode avalanche photodiode quad-cell arrays with crosstalk and dead time [J]. IEEE Sensors Journal, 2015, 15(4): 2133-2143. doi: 10.1109/JSEN.2014.2367235 [7] Wu Jin, Yu Xiangrong, Shi Shufang, et al. Infrared ranging technology by using single photon APD array readout integrated circuit [J]. Infrared and Laser Engineering, 2017, 46(6): 0604002. (in Chinese) [8] Deng S, Gordon D, Morrison A P. A Geiger-mode APD photon counting system with adjustable dead-time and interchangeable detector [J]. IEEE Photonics Technology Letters, 2016, 28(1): 99-102. doi: 10.1109/LPT.2015.2487342 [9] Chithra, Krishnapura N. A flexible 18-channel multi-hit time-to-digital converter for trigger-based data acquisition systems [J]. IEEE Transactions on Circuits and Systems I : Regular Papers, 2020, 67(6): 1892-1901. doi: 10.1109/TCSI.2020.2969977 [10] Maruyama Y, Blacksberg J, Charbon E. A 1024×8, 700-ps time-gated SPAD line sensor for planetary surface exploration with laser Raman spectroscopy and LIBS [J]. IEEE Journal of Solid-State Circuits, 2014, 49(1): 179-189. doi: 10.1109/JSSC.2013.2282091 [11] Cheng K H, Lo Y L. A fast-lock wide-range delay-locked loop using frequency-range selector for multiphase clock generator[J]. IEEE Transactions on Circuits and Systems II: Express Briefs, 2007, 54(7): 561-565. [12] Gersbach M, Maruyama Y, Trimananda R, et al. A time-resolved, low-noise single-photon image sensor fabricated in deep-submicron CMOS technology [J]. IEEE Journal of Solid-State Circuits, 2012, 47(6): 1394-1407. doi: 10.1109/JSSC.2012.2188466 [13] Zhu Zhipeng. Design of array readout circuit based on PLL-TDC[D]. Nanjing: Southeast University, 2019. (in Chinese) -

下载:

下载: