-

激光探测系统通过激光器发射光脉冲信号,精准感知目标的存在,具有探测精度高、抗干扰能力强等优势,应用于多种领域。随着微电子技术越加成熟,小型化已成为激光探测系统的关键技术和发展趋势[1]。

激光驱动电路板多由分立器件组成,且在板级设计中为了避免电磁干扰,器件之间需留有安全间距,所以传统激光器发射模块存在集成度低、面积大(13 mm×10 mm)等问题。Wang Jinhua等[2]提出使用CPLD替代TTL电路,减小了发射模块中控制电路的面积;Han Wei[3]等将激光器与驱动电路元件组装在AlN基板上,解决了驱动电源与激光器分离问题。但是以上两种方案中激光器驱动电路仍占据发射模块大部分面积。

由于激光探测发射模块中的驱动电路和功率MOSFET开关管占用面积过大[4],文中采用新型堆叠式封装形式,将栅极驱动管芯与功率MOSFET开关管堆叠封装,实现了发射模块最小化设计。芯片使用双面覆铜陶瓷基板替代引线键合连接两管芯,其中功率MOSFET管芯采用国产功率管裸芯。通过优化栅极驱动电路与版图结构,制作了小面积、高驱动能力的栅极驱动管芯。该多芯片封装形式减少了分立器件连接所需要的PCB板走线,降低系统分布式电感、电容效应,从而提高激光探测系统的可靠性和安全性。

-

虽然单管芯集成栅极驱动电路和功率MOSFET是集成度最高的方案,但是此方案目前只能使用单一工艺。功率MOSFET一般由垂直双扩散工艺加工,栅极驱动器多采用单片集成双极器件、CMOS器件以及高压MOS器件(Bipolar-CMOS-DMOS, BCD)工艺,所以很难将二者集成到单一管芯。文中提出的多芯片封装方案既有利于激光器驱动板小型化,又解决了两器件工艺不兼容的问题。

多芯片封装形式主要分为平铺式和堆叠式[5]。平铺式封装多采用引线键合工艺连接两管芯。该封装形式占用面积大,而且引线键合存在寄生参数大、载流量小等问题。文中选用3D堆叠式封装,并使用倒装技术,从而达到缩小面积、降低寄生参数、增强散热和提高功率密度的目的[6]。

-

功率MOSFET漏极从管芯背部引出,将其置于多芯片封装结构底层,可以增强散热能力。

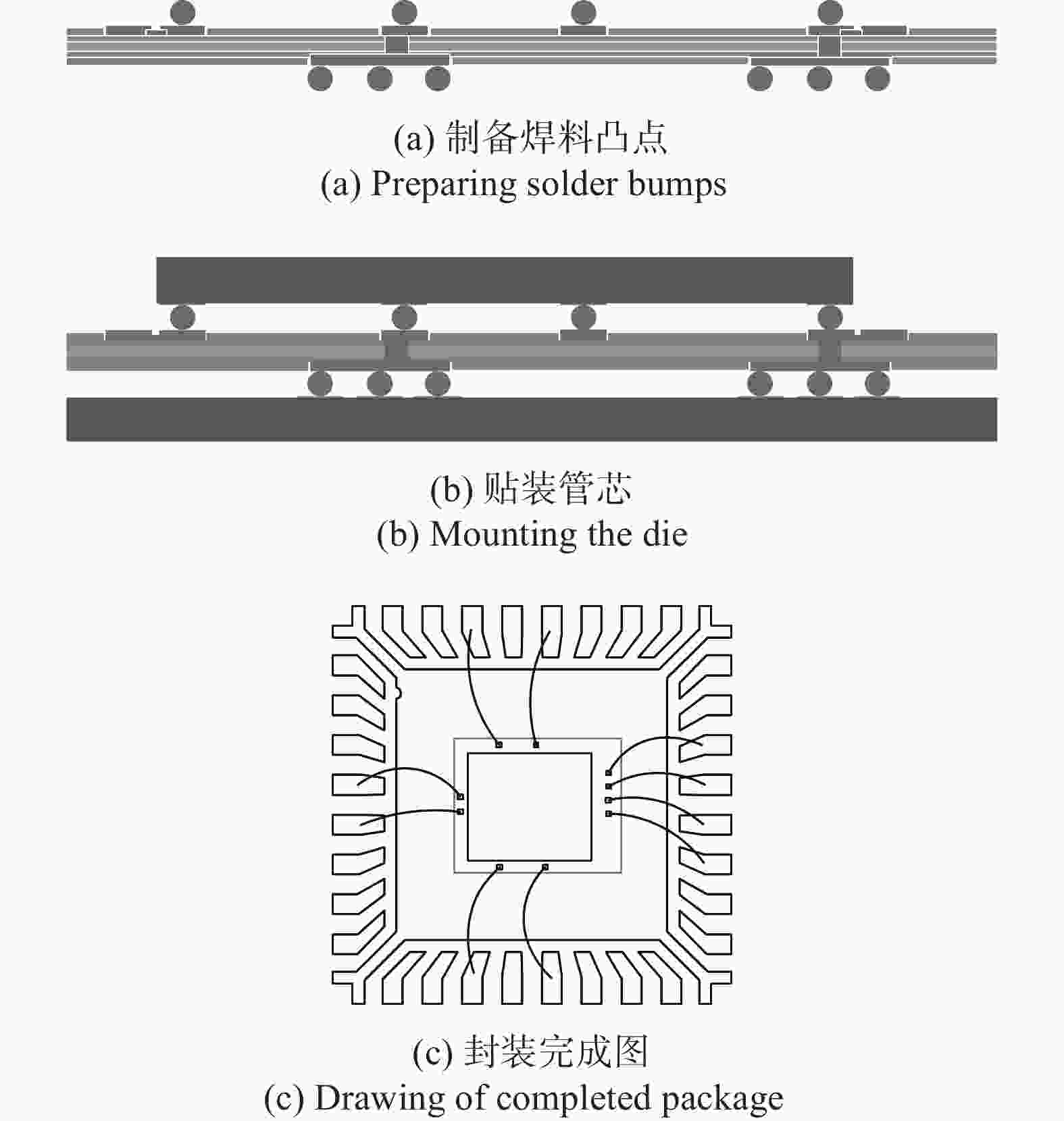

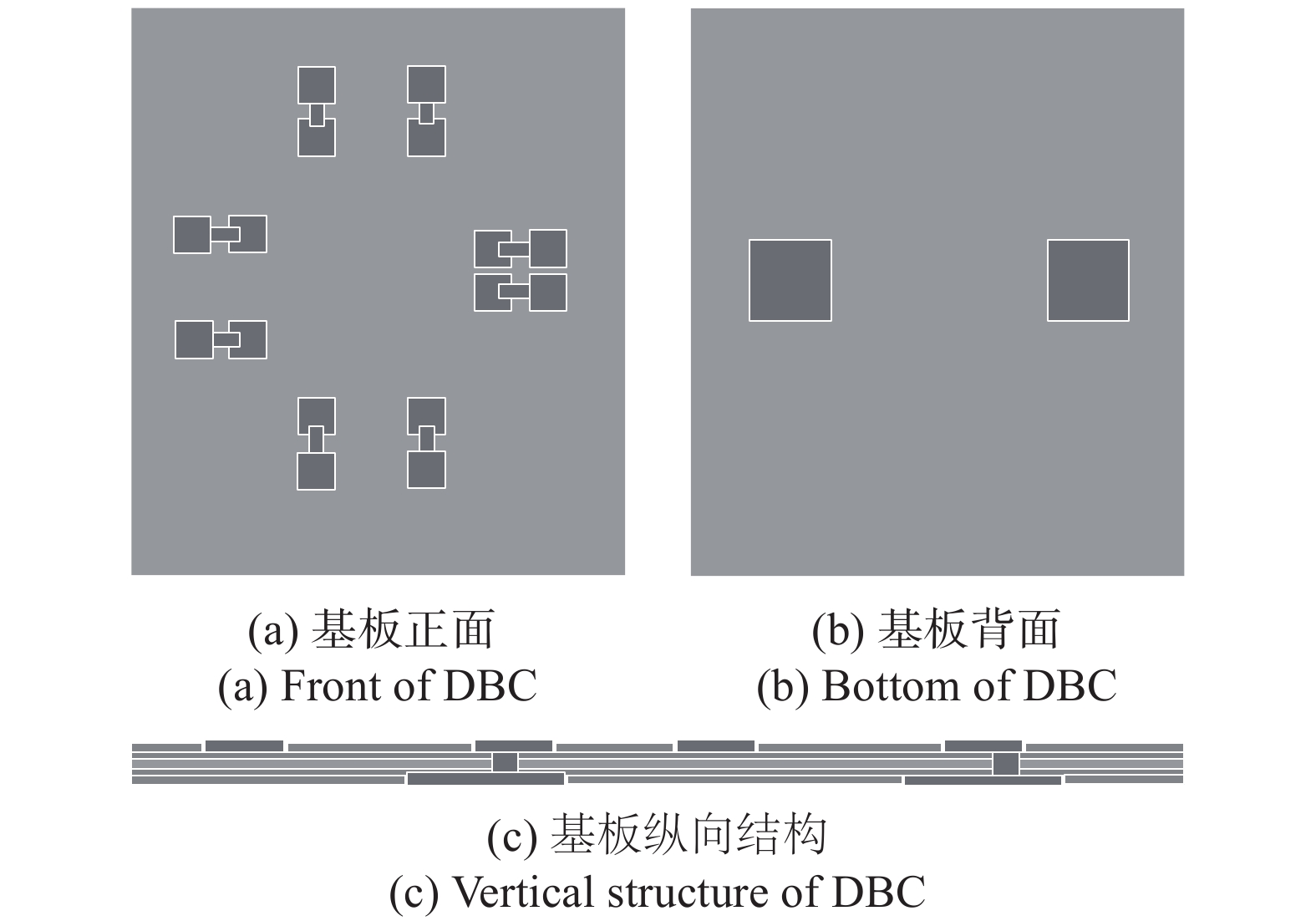

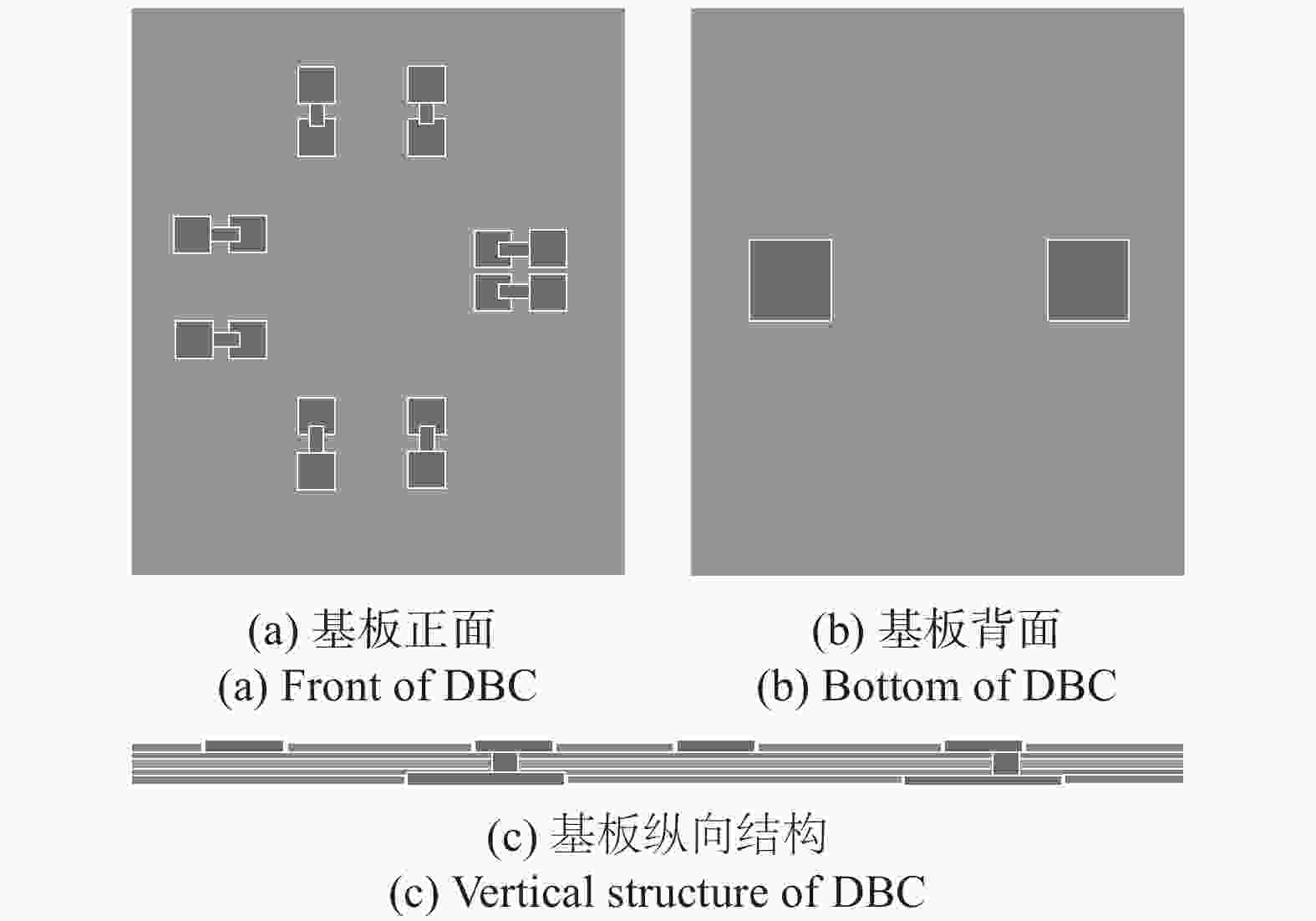

由于栅极驱动管芯面积比较小,如果将其直接倒扣在MOSFET管芯上,栅极驱动管芯其余焊盘很难引出。选择在两管芯之间增加覆铜陶瓷基板(Direct Bonding Copper, DBC),如图1所示。

中间层陶瓷基板预先刻蚀相应线路,并采用双层结构,通过分层布线设计使栅极驱动管芯焊盘位置重新排布。栅极驱动芯片的输入焊盘和电源焊盘从陶瓷基板正面引出,输出端焊盘从基板背面与功率MOSFET栅极连接。陶瓷基板不仅增强了芯片三维散热,也减小管芯内的电磁干扰。

-

如图2(a)所示,在中间层陶瓷基板的焊盘上制作焊料凸点。栅极驱动管芯与功率MOSFET管芯表面进行金属化处理后,分别贴装在中间陶瓷基板上,实现芯片与基板上相应焊盘的互连,使用回流焊工艺,完成所有焊接,如图2(b)所示。

芯片采用方形扁平无引脚封装,功率芯片漏极使用导电银胶,贴装在底部中央大焊盘处,可以使芯片承载大电流的同时增强散热能力。其余焊盘,使用引线键合方式连接到底部基板,如图2(c)所示。

-

硅基功率MOSFET产品已经十分成熟,选择国产某型号MOSFET作为激光器驱动芯片功率管芯,该管芯具有开关延时小,导通电阻低,输出电流大,面积小(约2 mm×2.3 mm)等优势;国内现有栅极驱动管芯存在面积大,性能较差等问题,所以有必要设计一款专用栅极驱动管芯与功率MOSFET管芯匹配,文中提出了设计方案,此方案在减小多芯片封装的寄生效应和增加封装可靠性方面进行了优化。

-

激光探测系统性能很大程度上取决于光脉冲质量,因此驱动芯片需要提供上升时间短、脉冲宽度窄的大电流脉冲信号[7]。表1给出了该栅极芯片的设计指标。在输出脉冲频率为10 kHz时,系统能有效且快速地探测到目标[8]。

表 1 栅极驱动芯片设计指标

Table 1. Design index of gate driving chip

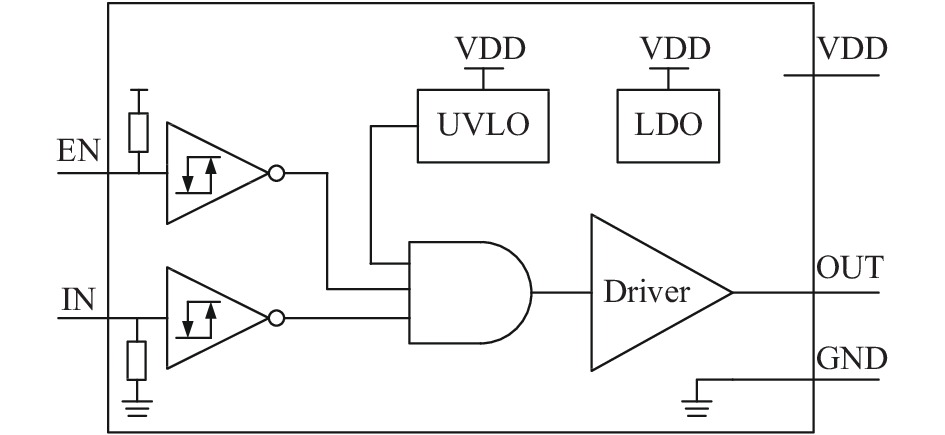

Frequency/kHz Pulse width/ns Rising and falling edge/ns Index 10 ≤200 ≤20 该栅极驱动管芯主要包括输入级、逻辑电路、输出级、低压线性稳压器(LDO)以及欠压保护五个模块,原理框图如图3所示。输入信号经过输入接口模块得到低压方波信号,该信号输入到逻辑控制模块,逻辑控制模块将其与欠压保护、启动保护等信号综合后,把得到的信号输出到驱动模块,由驱动模块产生驱动信号。

-

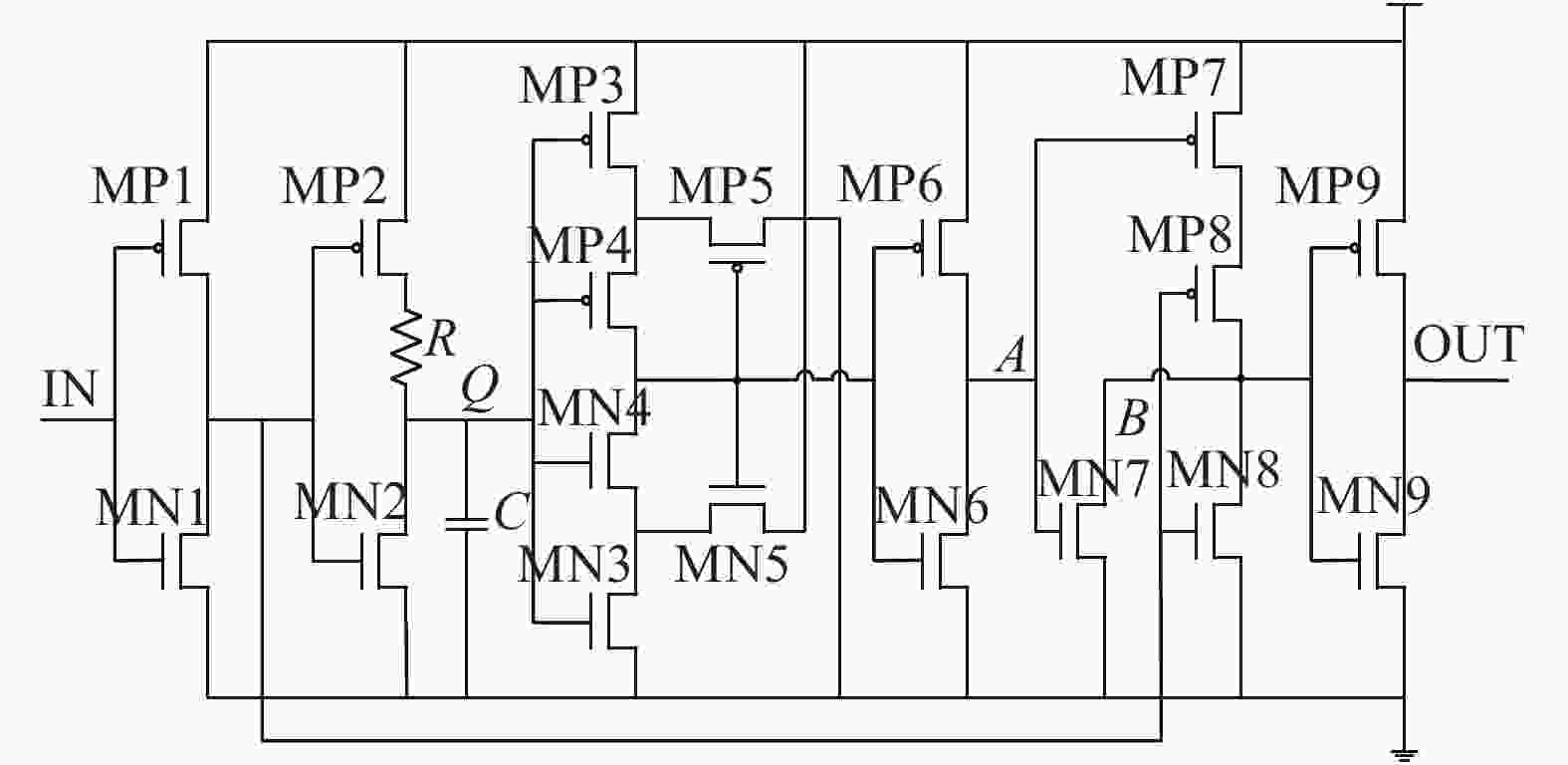

输入级接口电路使用施密特触发器,如图4所示,利用滞回效应提高系统抗噪和抗干扰能力。

输出脉冲宽度为:

$$ t=R\times C\times \ln\frac{{V}_{CC}}{{V}_{CC}-{V}_{T+}} $$ (1) $$ {V}_{T+}=\dfrac{{V}_{CC}+\sqrt{\dfrac{{\beta }_{3}}{{\beta }_{5}}}\times {V}_{TH}}{1+\sqrt{\dfrac{{\beta }_{3}}{{\beta }_{5}}}} $$ (2) 式中:

$ {\;\beta }_{3},\;{\;\beta }_{5} $ 为MN3,MN5的宽长比。 -

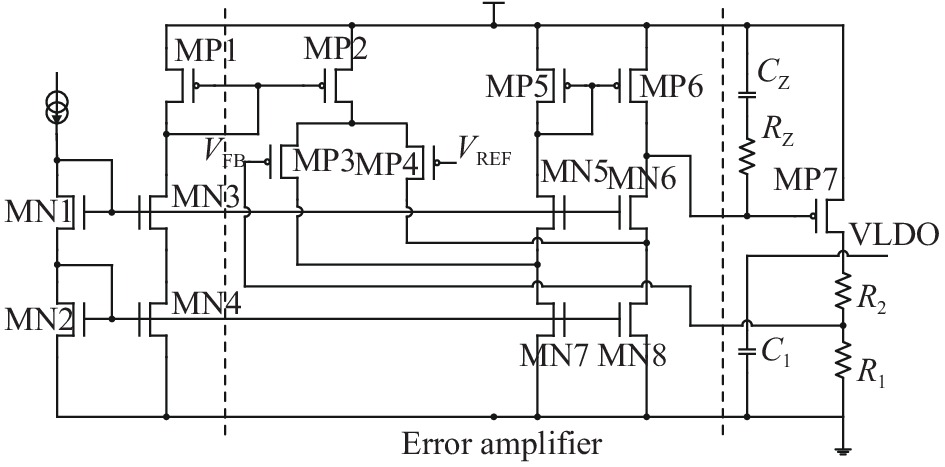

为了节省版图面积,该电路使用MP2-MP6,MN5-MN8管构成折叠共源共栅放大器,如图5所示,在电源与开关管MP7栅极之间串联RC,简化补偿网络。

-

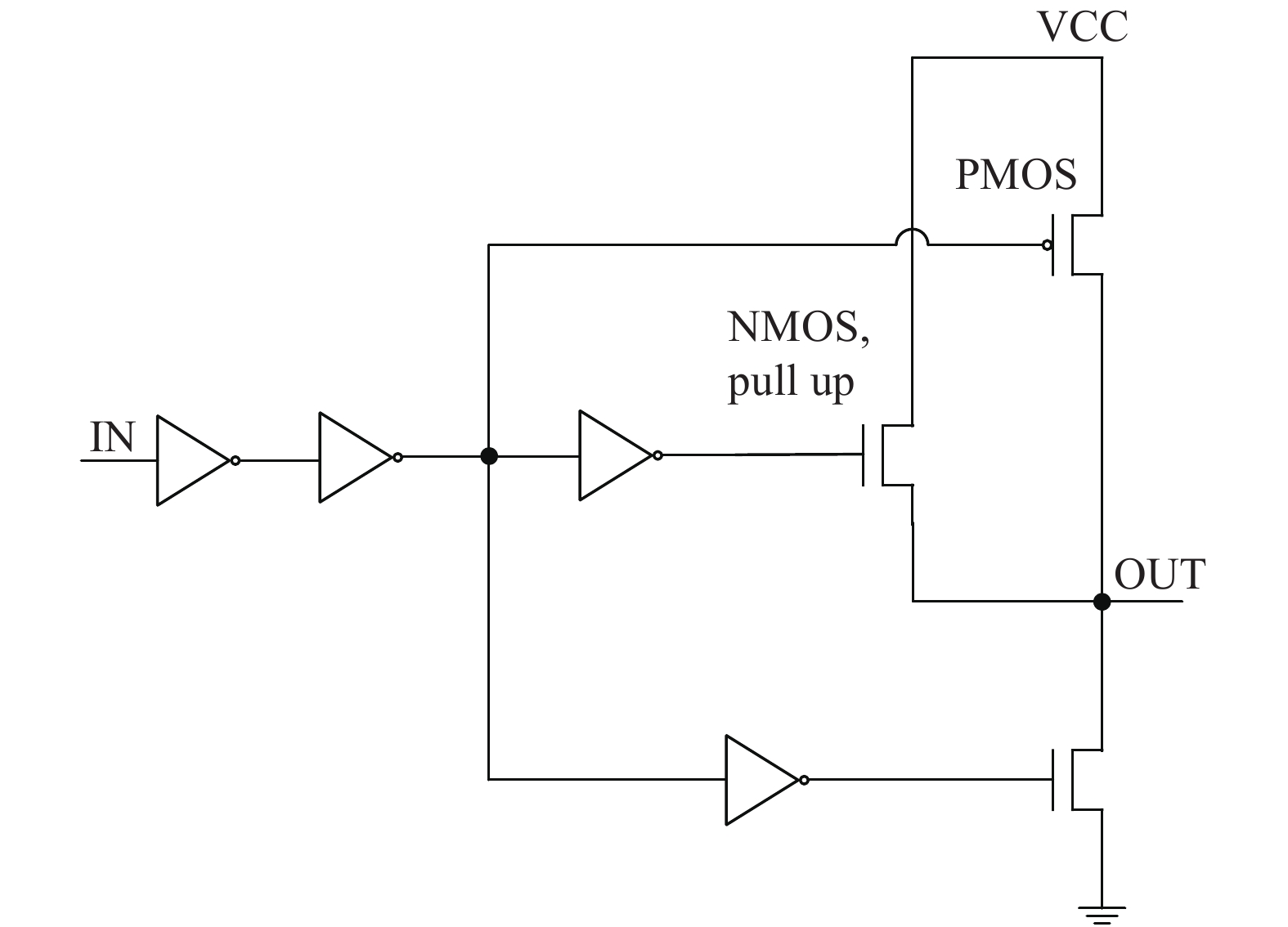

由于PMOS的沟道迁移率远低于NMOS,在提供相同电流输出时,PMOS元件所占版图面积很大。该电路在输出级增加了NMOS上拉结构,如图6所示,将N沟道MOSFET与P沟道MOSEFT并联,减小了管芯版图面积的同时,增加了输出驱动电流。

-

该栅极驱动管芯版图设计对寄生效应和过流能力方面进行了优化。

输出级版图位于整体版图右侧,缩短输出焊盘与MOSFET栅极之间的距离以减小寄生效应;增加栅极驱动输出焊盘尺寸,焊盘开窗100 μm×100 μm焊盘,以增强过流能力,提高多芯片的稳定性。栅极驱动管芯整体版图如图7所示,版图面积为1.7 mm×2 mm。该管芯采用0.25 μm BCD工艺加工制作。

-

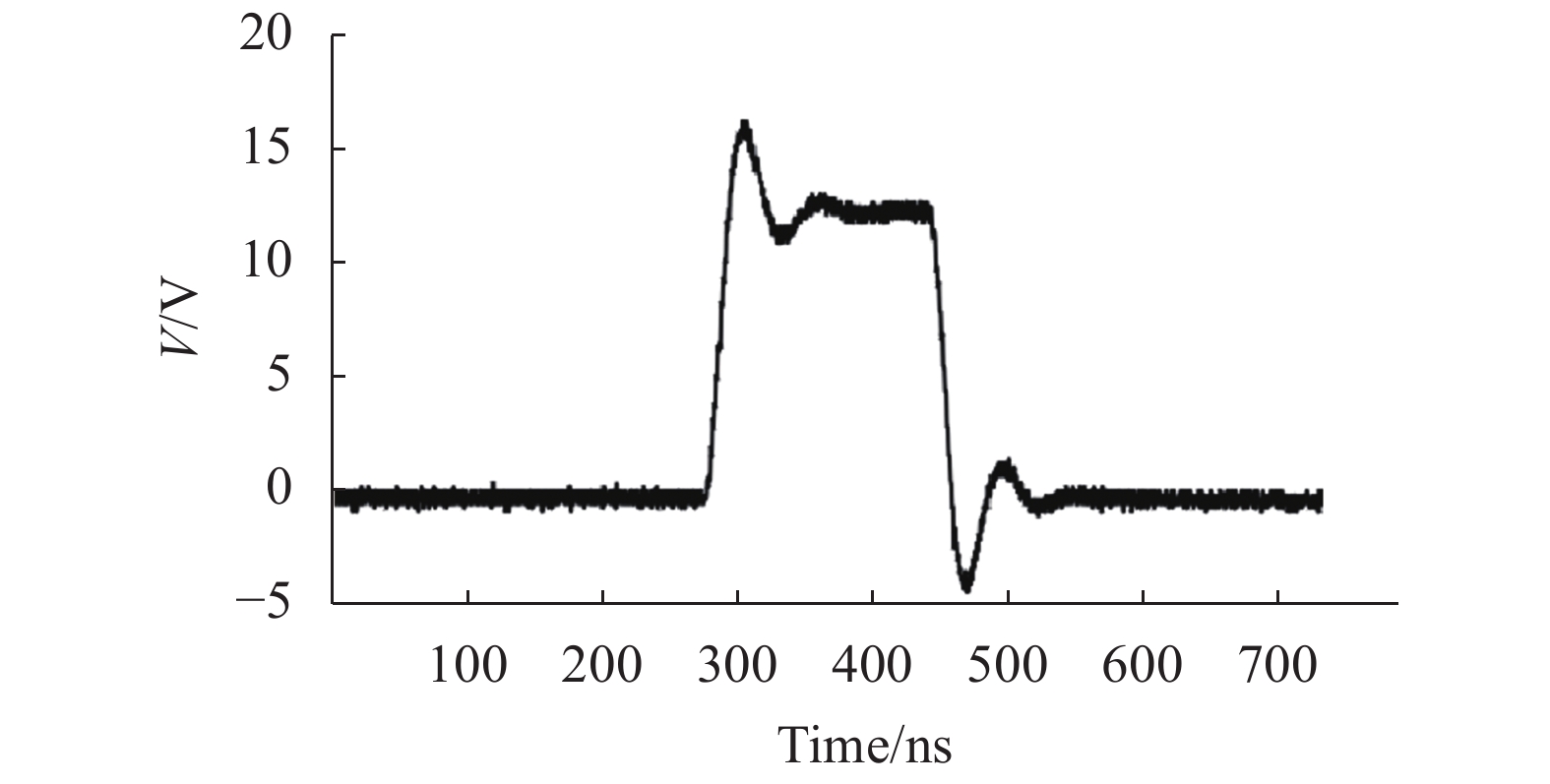

对栅极驱动管芯进行驱动能力测试,信号发生器的信号脉宽为100 ns,幅值为3.3 V,上升下降沿为3 ns,并采样1 nf电容作为负载以测试芯片驱动能力。

测试结果如图8所示,在供电电压为12 V时,输出脉冲宽度为160 ns,上升下降时间均小于20 ns,基本满足设计需求。测试结果与整体电路仿真结果相比,输出脉冲宽度比输入脉冲宽度略有展宽。

考虑其主要原因是电路中RC数值设计不理想。在芯片制造工艺中,不同工艺层的引入会产生相应的寄生器件。由于输入脉冲宽度较窄,器件寄生效应会更加明显,输入级电阻、电容值大于理论设计值,导致输出脉冲宽度展宽。解决方案是在电路设计时,重新计算电阻工艺误差,并建立仿真模型,以改善波形问题。

-

根据设计要求完成了激光驱动电路,制作了探测系统测试样机,如图9所示。

如图9(b)所示,该激光器驱动芯片对激光器进行驱动,屏幕显示激光器能够正常出光。采用光电探测器接收光信号,获得激光器光脉冲波形,如图10所示,并使用LP-3B激光功率计进行测试,测得该激光器单管芯最大峰值功率为18 W。

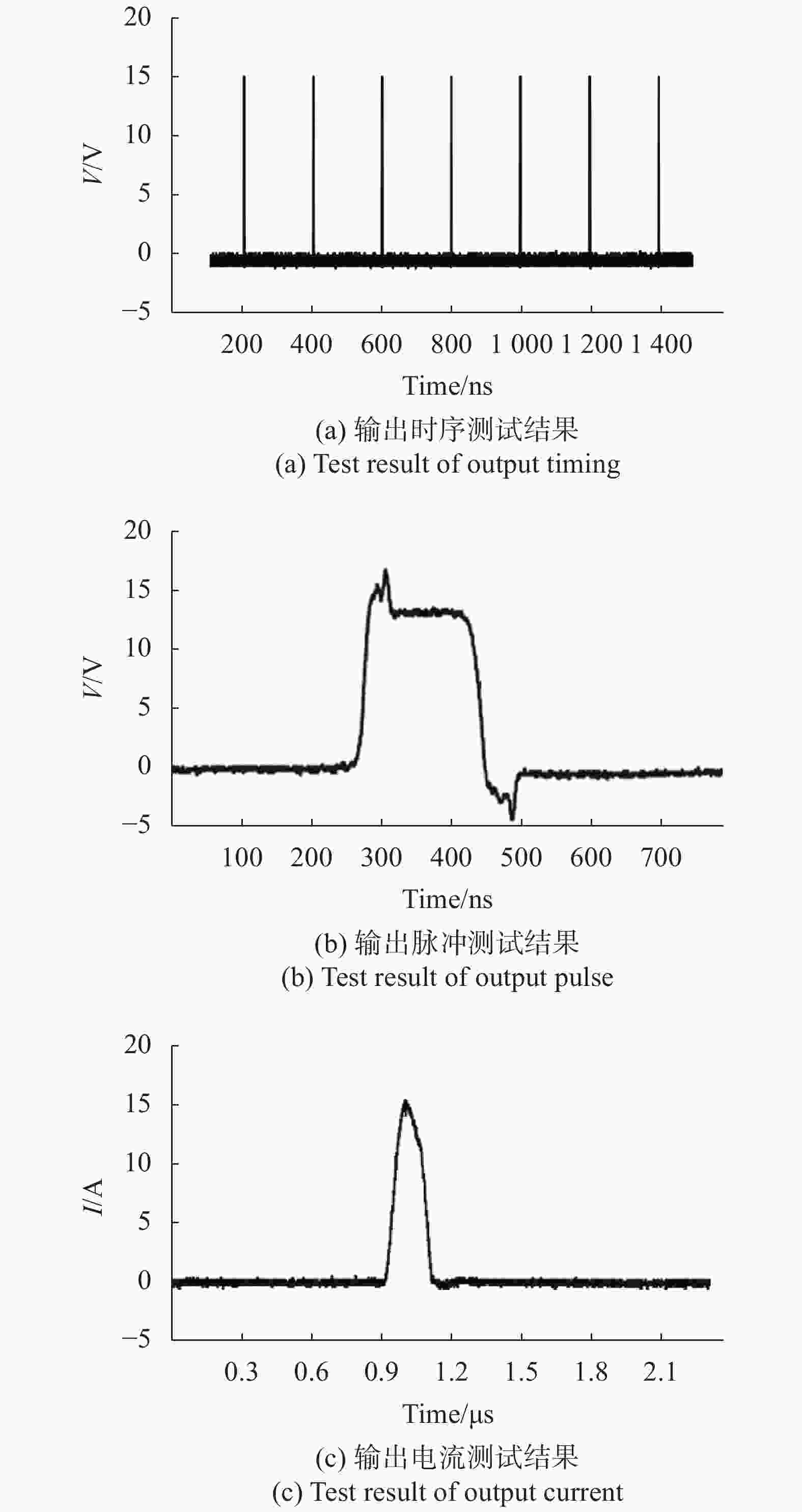

进一步测试激光器驱动芯片性能,提供输入电平为3.3 V、频率为10 kHz的PWM信号,在供电电压为12 V时进行测试。图11(a)为部分时序测试结果。由图11(b)可知,芯片输出脉冲宽度为180 ns的窄脉冲,其上升、下降时间小于30 ns,可见在该封装形式下,栅极驱动芯片能够使功率MOSFET的快速开启与关断。图11(c)为激光器驱动芯片输出电流脉冲波形图。将芯片输出端短路,使用100 mV/A电流探头进行测试,由图可见,驱动峰值电流可达15 A。该芯片可以通过调整功率开关管供电电压改变输出脉冲幅值与峰值电流大小。

激光器驱动芯片输出脉冲宽度较输入脉冲宽度展宽约20 ns。将栅极驱动管芯与功率MOSFET分离,并贴装在测试电路板上,再次进行测试后,脉冲宽度展宽现象消失。对多芯片封装模型分析可知,高封装密度使两管芯热耦合增强,陶瓷基板走线带来的寄生效应更加明显,导致输出波形展宽。将栅极驱动器输出级焊盘与功率MOSFET栅极焊盘通过DBC基板过孔直接连接,减小走线距离,同时采用陶瓷封装,进一步增强芯片散热能力,改善输出波形。

-

文中设计的激光驱动芯片具有超小面积5 mm×5 mm,实现了激光发射模块小型化,打破了驱动电路采用分立器件搭建的传统模式。该芯片使用新型3D堆叠式封装技术,在两管芯中间引入双面陶瓷基板,将栅极驱动器与功率MOSFET管芯集成,提高了系统集成度。经测试,芯片应用于激光探测系统,满足使用需求。

文中设计的激光器驱动芯片具有集成度高、驱动能力强等优点,可以通过改进驱动电路以及封装基板材料进一步提高驱动性能,可以应用于工业、通信等领域,同时该封装形式为功率集成电路(PIC)高度集成化提供了方向。

Design of high current narrow pulse laser driving chip

-

摘要: 脉冲式半导体激光器的出光质量直接影响探测精度。针对激光探测系统小型化的需求,设计一款面积小、集成度高的激光器驱动芯片。该芯片使用新型3D堆叠式封装技术将栅极驱动管芯与功率场效应晶体管管芯集成,并在中间添加双面覆铜陶瓷基板实现两管芯互连。该封装形式既提高了芯片的散热能力,又增强了过流能力。首先对激光探测发射模块现状进行详细介绍,引出了激光器驱动芯片的设计思路与方法,并给出了具体的封装设计流程。对栅极驱动电路与版图进行设计,使用0.25 μm BCD工艺制造栅极驱动芯片。在完成激光器驱动芯片封装后,搭建外围电路进行测试,使该芯片驱动860 nm激光器,芯片供电电压为12 V时,输入电平为3.3 V、频率为10 kHz的PWM信号,芯片输出脉冲宽度为180 ns的窄脉冲,其上升、下降时间小于30 ns,峰值电流高达15 A,可以使激光器正常出光,满足探测需求。芯片具有超小面积,约为5 mm×5 mm,解决了传统激光器驱动电路采用多芯片模块造成探测系统内部空间拥挤的问题,为小型化提供新思路。Abstract: The light quality of the pulsed semiconductor laser directly affects the detection accuracy. Aiming at the miniaturization requirement of laser detection system, a laser driving chip with small area and high integration was designed. The chip integrated the gate driving die and the power field effect transistor die using 3D stacked packaging technology, and added a double-side copper-clad ceramic substrate in the middle to realize the interconnection of the two dies. This packaging form not only improved the heat dissipation capability of the chip, but also enhanced the overcurrent capability. First, the current status of the laser detection transmitter module was introduced in detail, the design ideas and methods of the laser driver chip were introduced, and the specific packaging design process was given. Then, the gate driving circuit and layout were designed, and the gate driving chip was fabricated with a 0.25 μm BCD process. The multi-chip packaging scheme was designed. By setting up a peripheral circuit for testing to make the chip drive the 860 nm laser, the chip can output a narrow pulse with a pulse width of 180 ns, rise and fall times were less than 30 ns, and reached a peak current as high as 15 A when the chip power supply voltage was 12 V, the input level was 3.3 V and the frequency is 10 kHz PWM signal. It can make the laser emit light normally and meet the detection requirement. The chip has an ultra-small area about 5 mm×5 mm, which solves the problem of congestion in the internal space of the detection system caused by the traditional laser drive circuit using multi-chip modules, and provides a new idea for miniaturization.

-

Key words:

- semiconductor laser /

- driving chip /

- miniaturization /

- 3D packaging /

- power MOSFET

-

表 1 栅极驱动芯片设计指标

Table 1. Design index of gate driving chip

Frequency/kHz Pulse width/ns Rising and falling edge/ns Index 10 ≤200 ≤20 -

[1] Gao Yejun. Analysis of the research status and development process of fuze system in foreign countries [J]. Guidance and Fuze, 2018, 39(1): 1-5. (in Chinese) [2] Wang Jinhua, Chen Feixia. Design of realizing laser fuze circuits system miniaturization with CPLD [J]. Infrared and Laser Engineering, 2000, 29(4): 67-70. (in Chinese) [3] Han Wei, Zheng Xiang, Zhao Baiqin. Design of miniaturized transmitting-receiving system for laser detection [J]. Infrared and Laser Engineering, 2017, 46(9): 0906008. (in Chinese) [4] Chen Shanshan, Zhang He, Xu Xiaobin. Design of narrow pulse light source driving circuit of laser fuze [J]. Infrared and Laser Engineering, 2018, 47(S1): S106004. [5] Yang Jiansheng. Development of three-dimensional memory die stack packages technique [J]. Equipment for Electronic Products Manufacturing, 2018, 47(47): 40-44. (in Chinese) [6] Tong Zhiyi. The present situation of high-density packaging and its future [J]. Equipment for Electronic Products Manu-facturing, 2000, 29(2): 1-9. (in Chinese) [7] Cong Menglong, Li Li, Cui Yansong, et al. Design of high stability digital control driving system for semiconductor laser [J]. Optics and Precision Engineering, 2010, 18(7): 1629-1636. (in Chinese) [8] Dai Qin, Song Wenwu, Wang Xijun. Design and stability of high frequency LDs driving circuit [J]. Optics and Precision Engineering, 2006, 14(5): 745-748. (in Chinese) -

下载:

下载: