# 资源有限FPGA 的多通道时间-数字转换系统

吴 军,王海伟,郭 颖,洪光烈,何志平,徐卫明,舒 嵘

(中国科学院上海技术物理研究所 空间主动光电技术与系统实验室,上海 200083)

摘 要:基于 Xilinx XC2V3000 芯片设计了一种应用于星载多通道快速激光三维成像雷达中的抗辐 照增强型时间-数字转换(Time-to-Digital Converter, TDC)系统。单板 2 片 FPGA 内实现了 16 通道高 精度时间间隔测量。采用了多延时链冗余结构,每个测时通道由3个物理测时链路组成,最后通过三 模冗余增强抗单粒子翻转能力。并应用了通道均匀性校准修正技术,解决了多通道测时均匀性问题。 实验结果表明,系统测时精度达到 62.9 ps,通道一致性较好,满足激光雷达三维成像要求,同时该技 术方案具有低功耗、轻量化等特点。

关键词:激光三维成像雷达; 时间-数字转换系统; 空间应用; 资源有限; 三模冗余 中图分类号: TN959.74 文献标志码: A 文章编号: 1007-2276(2015)04-1208-10

# Resources-limited FPGA based-multi-channel TDC system

Wu Jun, Wang Haiwei, Guo Ying, Hong Guanglie, He Zhiping, Xu Weiming, Shu Rong

(Laboratory of Space Active Electro-Optical Technology and Systems, Shanghai Institute of Technical Physics, Chinese Academy of Sciences, Shanghai 200083, China)

Abstract: Based on Xilinx XC2V3000 chip, a multi-channel irradiation resistance enhanced (Time-to-Digital Converter, TDC) system was designed. 16-channel high-precision time measurement was achieved within 2 FPGAs in a single board. With multi-redundant delay-chain structure, each measuring channel consisting of three physical timing links, and the anti-SEU ability was enhanced by triple modular redundancy. The channel uniformity calibration correction technology was applied to solve the multichannel uniformity issues. Experimental results prove that the system meets the requirements of a 3D imaging laser radar, with an accuracy of 62.9 ps and a good uniformity. Meanwhile, the technical solution provides has a character of low power consumption, light weight etc.

Key words: 3D imaging laser radar; TDC system; space applications; resources-limited; triple modular redundancy

收稿日期:2014-08-05: 修订日期:2014-09-15

基金项目:国家科技支撑计划课题-机载激光雷达和高光谱成像仪组合系统(2012BAH34B02)

作者简介:吴军(1988-),男,博士生,主要从事激光遥感探技术方面的研究。Email:ahcolin@163.com

导师简介:舒嵘(1971-),男,研究员,博士生导师,主要从事空间光电遥感技术方面的研究。Email:shurong@mail.sitp.ac.cn

# 0 引言

高精度 TDC 技术在核物理、高能物理试验、激 光测距、医学影像、通信、导航定位等领域已经广泛 应用。数字型 TDC 技术具有高可靠性、高集成性和 低功耗等优点,随着大规模集成电路技术的发展,基 于 ASIC 和 FPGA 的数字型 TDC 技术成为发展趋 势。由于 FPGA 具有可重配可定制特性, 所以基于 FPGA的 TDC 技术逐渐成为研究热点。早在1997年、 Kalisz 等在 QuickLogic 的 FPGA 内获得了 200 ps 的 精度<sup>[1]</sup>:2002年, Andaloussie 等在一个 XCV300 的 FPGA 内实现了 150 ps 的精度 [2];2005 年 Xie DK 等使用级 联链实现了 75 ps 的精度[3]; 2006 年 Song Jian在多款 器件内利用加法器生成的进位链作为延迟链,达到 了较好的效果[4],后续设计多数也基于进位链更进一 步改进,为提高精度通常选用速度更快的器件;2008 年 Wu Jinyuan 提出了 Wave UnionA(B)方式,是一种 两次(多次)测量求平均的方式,通过这种方式,测量 精度能超过器件固有的延迟所能达到的精度;2010 年 Daigneault M 提出了一种并行的多路延迟线测时 方式,采用 10 路并行测量达到了 24 ps 的 RMS 测时 精度<sup>[5]</sup>;2011 年 Wang Jinhong 对多次测量求平均可以 达到的最好的效果进行了理论分析及仿真,在 Virtex 4 内用 Wave Union B 方式作 4 次平均测时达 到 9 ps 的 RMS 精度[6];后续的很多工作多是采用高 等级器件实现多通道的时间测量以及使用多次求平 均的方式获得更高的时间测量精度。采用延迟线内 插技术在 FPGA 内部实现高精度的时间测量的方案 占用较少的外部资源,具有时间分辨率高、精度高、 动态范围大可定制、成本低、可移植性和扩展性强等 优点。

近年来国内在星载激光雷达、星地量子通信、星载空间粒子探测以及卫星导航定位等方面都取得了长足的进步,但也同步对空间应用 TDC 技术提出了新要求同,突出表现为多通道、低功耗以及抗辐照能力方面的特殊需求。如 ACAM 公司专用测时芯片TDC-GPI 的 LET 阈值低于 25 MeV·cm²/mg,不适合应用于长期在轨场合,而普通 SRAM 型 FPGA 器件同样为单粒子敏感器件。目前解决途径主要是采用反熔丝型 FPGA 和采用基于抗辐照型 SRAM 再进行

三模冗余。反熔丝型 FPGA 在抗单粒子特性方面具有良好的表现,但是其内部延时单元粒度相对较粗,且资源占用较严重,在 AX500 FPGA 内实现 4 通道占用了约 55%的资源<sup>[8]</sup>,且调试复杂。为此,文章结合星载快速激光三维成像雷达的高精度、低功耗以及轻量化需求提出了一种基于 XC2V3000 FPGA 抗辐照增强型 8 通道 TDC 技术方案。该技术方案在有限逻辑资源条件下采用三通道冗余设计架构,针对密集测时通道资源优化、多通道非均匀性校正、译码逻辑优化等开展重点研究,最后经测试实现了 62.9 ps的 RMS 测时精度,能够满足激光雷达静态测距精度要求,两片 FPGA 可以共同实现 16 通道测时。该技术方案也为未来高精度 TDC 技术的其他空间应用提供了有效的技术途径。

# 1 基于 FPGA 的 TDC 技术

抽头延迟线技术是一种时间测量方法,信号在延迟线上随时间流逝而传播(图 1(a)),通过分析信号传输的情况则能得出时间流逝的情况。如果能很快地保存延迟线上某个时刻的状态(图 1(b)),并且随后快速精确地分析延迟线上的信号并推算出时间,则可以提高时间测量的精度、减小测量的死时间。

图 1 信号在延迟线上传播(a)及快速保存信号传播情况(b)

Fig.1 Signal propagation on the delay line (a) and fast saving of the signal propagation status (b)

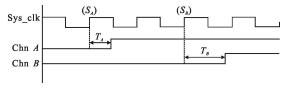

这种方案的主要思想是将时间间隔分为粗时间测量和细时间测量。如图 2 所示,两个信号 A 和 B。分别对这两个信号与系统时钟上升沿的时间差(细时间)进行精确测量,即  $T_A$  和  $T_B$ 。然后分别记下这两处的时钟计数,即  $S_A$  和  $S_B$ 。

图 2 粗细时间结合测量

Fig.2 A combination of coarse and fine time measurements

则 A、B 两个信号的时间差即可按公式(1)进行

计算。

$$T_{\text{DIFF}} = T_B - T_A + |S_A - S_B| \times T_{\text{SYS}} \tag{1}$$

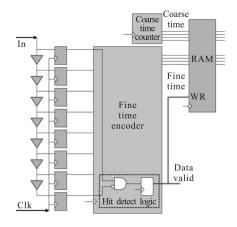

式中:  $T_{SYS}$  为系统时钟周期;  $S_A$ 、 $S_B$  为时钟计数器的计数值。高精度的时间测量的主要工作则主要集中在细时间  $T_A$  和  $T_B$  的测量上。图 3 为基于 FPGA 的延时链的典型的时间测量模块框图<sup>[9]</sup>。

图 3 典型的基于 FPGA 的 TDC 系统结构图 Fig.3 Typical block diagram of FPGA based TDC

脉冲信号在延时链内被延时,在延时链上的传递情况在时钟信号 CLK 的边沿被触发器锁存,通过后续的脉冲判断逻辑 Hit Detect Logic 判定信号到来,通过 Encoder 将寄存器内信号的边沿进行编码,由于延迟链上的延迟并非完全线性,且各通道存在

差异,使用 RAM 作为一个查找表,完成相应的时间 校正,粗计数器统计时钟个数,并将脉冲有效时的计 数器数值锁存。

# 2 激光三维成像雷达多通道 TDC 系统硬件框架

星载快速激光三维成像雷达采用 16 通道高速并行扫描的工作体制,激光雷达接收机负责接收 16 通道回波信号,由 16 通道探测前放电路和多通道测时系统构成。多通道测时系统由回波数字化单元和 TDC单元组成。激光发射主波信号(Main Pulse)以及回波信号(Echo Pulse)先后输入到 TDC单元完成激光脉冲飞行时间高精度测量,最终实现三维距离成像。

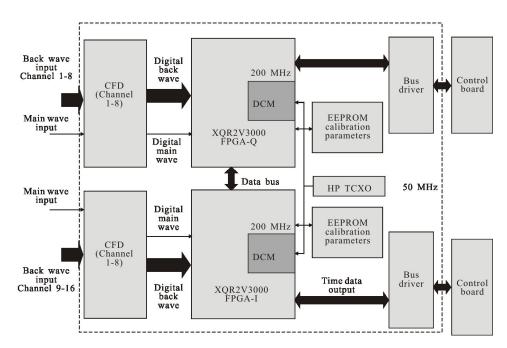

16 通道多路冗余抗辐照增强型 TDC 技术方案 如图 4 所示,2 片 FPGA 实现 16 通道激光脉冲飞行 时间的测量,相比于以往 16 片 TDC-GP1 芯片实现 16 通道激光雷达的方案,其集成度更高,能够达到 轻量化设计目的。

图 4 中,16 通道 TDC 系统由两片 FPGA 芯片及外围器件构成,选用型号为 TH-2Q3-50 MHz 的高精度温补晶振为 FPGA 提供频率温漂系数为±1 ppm/℃的时钟基准,利用 FPGA 的DCM 产生 200 MHz 时钟基准。EEPROM 芯片存储 FPGA 各通道不同温度条件

图 4 16 通道 TDC 方案框图

Fig.4 Block diagram of 16-channel TDC

下绝对和相对的校准参数,用于校正各通道的测量绝对值和各通道间的均匀性。

# 3 激光三维成像雷达多通道 TDC 软件系统设计

16 通道抗辐照增强型 TDC 系统最终选用具有 多次成功在轨飞行经历的 Xilinx 公司 Virtex II 系列 宇航级 XQV2C3000 芯片,该系统中先选用工业级 XC2V3000 芯片进行试验。相比于 Virtex 4/Virtex 5系列,该 FPGA 速度慢、延时链资源有限且逻辑资源紧张,单列可用最大延迟链长度为 128、共 112 列,这导致了 TDC 多通道在逻辑设计实现和时序约束优化方面难度提升。

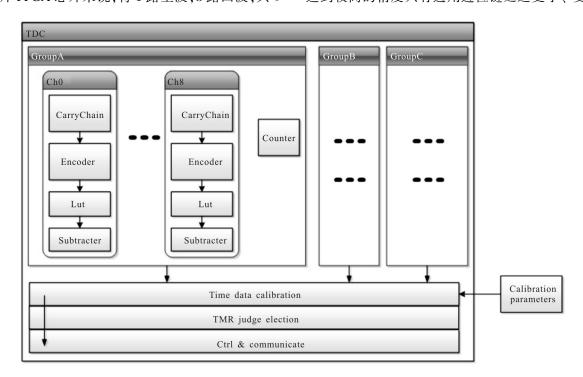

对于 SRAM 型 FPGA 的空间应用,需在选择宇航级抗辐照型 FPGA 基础上进一步完成"三模冗余" (TMR, Triple Modular Redundancy) 设计以达到抗单粒子能力增强的目的。但对 TDC 特殊应用,考虑到延时链单元级三模冗余会严重影响延时链布局,而译码逻辑单元级三模冗余也会明显降低系统工作频率导致译码错误,本系统针对上述问题提出了一种功能级三模冗余设计方案。图 5 为系统设计方案。对于单片 FPGA 芯片来说,将 1 路主波,8 路回波,共 9

路信号作为一个测量组。三模冗余即采用同样结构 的3组测量模块,分别为 GroupA、GroupB、GroupC, 均对9路脉冲信号进行测量。3组输出的数据经路径 固有误差进行数据校准(Calibration parameters 和 time data calibration)及三模判决(TMR judge election)给出 准确的时间测量值后,最后由通信控制模块(Ctrl & Comunicate)输出。每个组内由 9 个测时通道(从 Ch0 到 Ch8,其中 Ch0 为主波)、一个粗计数器和时间锁 存 RAM 模块构成,其中粗计数器用来统计主波到来 后的时钟个数,由主波信号触发,时间锁存 RAM 模 块在主波到来 16 μs 后存储本组测量的所有时间数 据。每个测时通道分别包括进位延时链(CarryChain)、 译码器(Encoder)、校准查找表(Lut)、减法器(Subtracter) 等模块,其中校准查找表用来校正延迟链的非线性, 减法器用来计算主波测量的结果和当前通道测量的 结果的时间差。

对于延迟链的生成,目前主流的做法是利用进位链进行延迟。早期是在一个被测脉冲产生一个信号前沿,在进位链内传播[10]。Song Jian 在 Virtex II 芯片上测得延迟单元大小将近 69 ps<sup>[10]</sup>。延迟单元的大小、非均匀性决定了所生成的 TDC 通道的精度,要达到较高的精度只有选用进位链延迟更小、更均匀

图 5 三模冗余下的 8 通道时间测量模块框图

Fig.5 Block diagram of a 8-channel TDC module in TMR mode

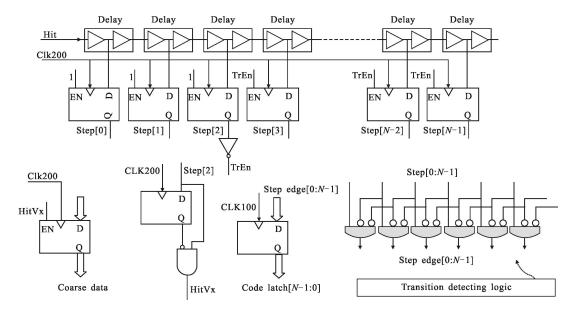

的高等级的器件。后期在一些高精度场合时采用 Wave Union 方式产生多个信号前沿以提高测时精度<sup>[11]</sup>,但后续译码及处理更加复杂。 该系统采用 XQV2C3000,需要用更少的资源在 速度较慢的器件上实现稳固可靠的时间测量,应采 用只产生一个信号前沿的方式。图 6 为该系统所采

图 6 该系统采用的延迟链结构及寄存器结构

Fig.6 TDC system with delay-line structure and register structure

用延迟链结构及寄存器结构。

信号在延迟单元内传递,Virtex II FPGA 内部一个 Slice 包含 2 个进位结构,可以将两个进位结构作为两个延迟单元,也可以作为一个延迟单元,作为两个延迟单元则精度会提高<sup>[12]</sup>,但是延迟单元数目加倍,该系统使用两个进位结构作为一个延迟单元(Delay)。

因 XC2V3000 资源较少,延迟链长度有限,最多只能实现 128 个延迟单元,而实现时应保证整个延迟单元大于一个时钟周期。Song Jian 在其论文中指出 Virtex II 在 100 MHz 的时钟下,延迟单元至少需要 138 个[10]。故该系统只能以较高的时钟频率运行,以降低链长。Virtex II 运行速度并不快,以较高速度运行容易出现时序不满足。

该系统以 200 MHz 时钟作为延迟链后的寄存器的触发时钟以减少链长。当采用 200 MHz 时钟时,周期为 5 ns,假设延迟单元延迟为 69 ps<sup>[10]</sup>,需要 72 个延迟单元,考虑到延迟单元随器件变化的可能性,本系统设计链长为 96 个单元,相对于 100 MHz 的时钟已经有效减少链长,减少了资源使用量。采用尽量少的资源,用 200 MHz 时钟对 Virtex II 内 96 个单元进行译码并不现实,时序难以满足。故该系统采用带有

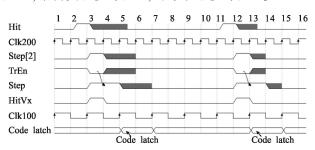

使能的触发结构,使有效的回波信号在延迟链上延时的情况在寄存器上保留两个或两个以上的周期,再使用 100 MHz 的时钟 CLK100 进行信号的锁存及处理,结构实现参考图 6,时序效果参考图 7。

图 7 延迟链信号锁存时序图

Fig.7 Timing diagram of delay-line signal latching

图 7 中,脉冲信号相对于 CLK200 时钟(200MHz)、CLK100 时钟(100 MHz)有两种关系。CLK200 时钟信号进行锁存时有两种状态,一种是在 CLK100 低电平时(第 1 个脉冲),另外一种是在 CLK100 高电平时(第 2 个脉冲)。图 7 中,脉冲信号 Hit 脉宽可能稍大于一个 200 MHz 时钟周期,或大于多个 200 MHz 时钟周期(图中用阴影部分表示)。信号到来时,相应的使能信号为一个周期或多个时钟周期,可以实现

Step 信号多保留一个或多个 (图中阴影部分)200 MHz 时钟周期。

图 6 中,延时链后紧跟着寄存器,理想情况下延迟链到寄存器的延时大小一致。但实际物理结构并不能保证该延迟大小一致。理论脉冲前沿处锁存数据为"111000"形式,其中 1->0 跳变为脉冲前沿,而实际情况可能出现"110100"形式,容易误认为有两个 1->0 跳变沿。采用图 6 所示的"Transition Detectin Logic"逻辑可以有效解决该问题<sup>[9]</sup>。该逻辑针对"100"组合进行验证,以达到有效判别信号前沿。

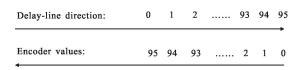

对于延迟链的译码,如图 8 所示,信号在延迟链内如图所示由左向右传播,并将其延迟标上序号 0~95。对于译码的值,则应反过来,延迟链进入端为大值,而远端为小值。该设计可以这样理解:当一个时钟前沿到来时,信号在延迟链上传播的越远,其到达时间越早,则其相对于上一个时钟前沿的时间应该越小。

图 8 延迟链方向及对应的译码值大小关系

Fig.8 Relation between the delay-line direction and the encoder value

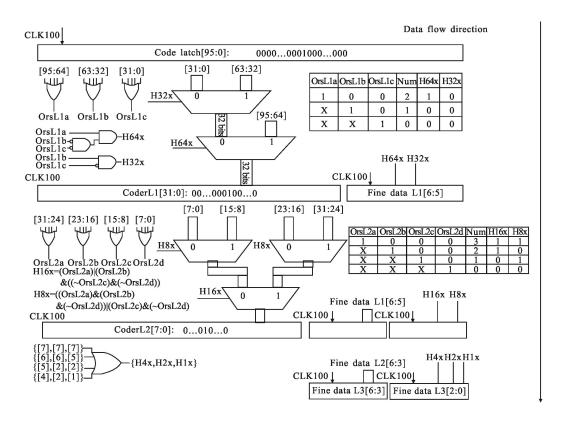

## 3.1 TDC 系统高速译码单元

在 TDC 实现中,译码是一个重要组成部分。译码器的优劣直接影响着系统的运行速度及资源的占用量,这是本系统需要重点考虑的部分。

为在速度慢、资源少的器件内实现译码,采用图9所示流水线译码方案。从信号进入到最终译码输出分三级流水线,每一级组合延迟较小,译码单元可以以100MHz时钟稳定运行。译码器第一级将96位分为3组,通过图9中的真值表选通输出32位有效

图 9 三级流水高速译码器框图

Fig.9 Block diagram of 3-stage pipelined high-speed encoder

数据段,第二级再将有效数据段分为4组,经真值表逻辑判断输出8位有效数据段,第三级进一步得出

最终结果。通过几级流水减少对数据量的占用,可以 有效降低对寄存器和组合逻辑资源的占用。

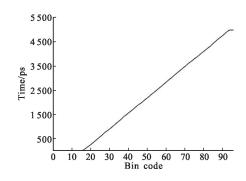

#### 3.2 延迟链校准

对于每个延迟单元 bin 的大小,每片 FPGA、每条延迟链、每个延迟单元均会存在不同。要得出精确的时间数据,必须对延迟链的延迟情况进行校准。计算延迟单元大小的方式有两种,一种是平均延迟(average delay)大小的方法,另外一种是计算出每个延迟单元的延迟(bin-by-bin)大小进而生成一个查找表对每个单元进行校准。

平均延迟方案假设每个延迟单元延迟大小相同[18],一条链的总延迟时间被设计成稍长于一个时钟周期  $t_p$ 。一个输入信号的变化可能会被记录两次,设这两次记录的位置是  $N_1$ 、 $N_2$ ,则每个延迟单元的平均延迟为公式(2):

$$t_d = \frac{t_p}{N_1 - N_2} \tag{2}$$

平均延迟方案没有对每个延迟单元进行精细校准,尤其有些延迟单元的大小变化较大时,该方案会造成较大的测时误差。

该系统采用 bin-by-bin 方式对延迟链进行校准。利用 ADC 测试中标准的码密度测试(Code Density Test, CDT)方法可以对每个延迟单元大小进行测试[14]。产生足够多的在测量动态范围内平均分布的随机信号给 TDC,并把读出的数据做直方图统计,该直方图每个 bin 中统计的数目正比于 TDC 实际的 bin 延迟宽度,进而得出延迟单元的延迟宽度。CDT 需要的随机信号不容易得到,可采用高精度信号发生器的时钟产生 hit 信号,让信号源与 TDC 的时钟信号源时钟不相关,如前者为 5.11 MHz,后者 50 MHz [14]。假设所有 TDC 延迟单元 bin 的延迟大小均被测量并被存储为一个数组  $\omega_k$ 。则第 n 个延迟单元所对应的时间  $t_n$  可表达为公式(3)[9]:

$$t_n = \frac{\omega_n}{2} + \sum_{k=0}^{n-1} \omega_k \tag{3}$$

对于经译码器得出的延迟单元的位置,即可相应地求出其所对应的延迟时间。

该系统采用 ROM 作为查找表(Lut)对延迟链信息进行校准。系统在特定温度下实现校准,在校准模式下,原始进位链位置数据直接输出,并生成校准数据,再将校准数据导入 ROM 内,系统以实测模式工作。

对 Virtex II 器件, Jian Song 对其温度变化和电压变化对 TDC 的影响进行了测试<sup>[4]</sup>。测试结果表明,

温度在 10°~30°变化时,TDC 的表现几乎没有任何变化。同样,电压的变化在正常供电电压的±5%以内,TDC 的表现也没有太多的变化。该设计的实测情况跟 SongJian 所分析一致。另外该设计最终会使用在恒温环境下,很大程度上减小了温度变化带来的影响。

#### 3.3 多通道布局与三模冗余设计

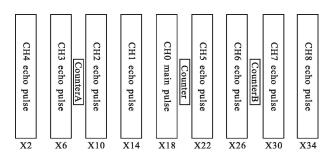

为实现 8 通道回波测时,需在 112 列 Slice 里实现 27 路时间测量链路,每路 TDC 只能占用 4 Slice 资源。各通道间的分配需要充分考虑路径延迟以保证时序,也需要对每组延迟不一致进行固有走线延迟进行校准以便于 3 组结果进行判选。该方案的三模冗余模式采用的 3 组测量模块 GroupA、GroupB、GroupC的布局见图 5,每一组分为 1 路主波,8 路回波。而对每组内的布局如图 10 所示(图中 CH4 回波下侧的 X2 表示当前通道所在 FPGA 内资源处于第 2 列 Slice,其他列类似)。

图 10 GroupA 下的资源分配

Fig.10 Resource assignment in GroupA

图 10 中,每一组用一个专用的计数器"Counter", 当主波到来时计数器清零再重新计数。考虑到尽量 减小计数器结果的传输延迟,将主波置于 9 路通道 的中间。而将其他 8 路前 4 路置于主波左侧,后 4 路 置于主波右侧。如图,Counter 的结果直接传输给 CH4,由于空间仍相隔 20 个 Slice,延迟依然相当大, 大于 200 MHz 时钟对应的周期 5ns。故分别设置两个 中继的寄存器,"CounterA"、"CounterB",分别减小寄 存器间的路径延迟,使 Counter 可以运行在 200 MHz 时钟下。

布局布线不可避免的会带来走线固有延时偏差。对同一个回波通道,三组测量链路的结果存在固定偏差。图 4、图 5 是采用外置 EEPROM 对 3 个通道的结果进行校准修正,根据高低温试验结果,在-20~65  $^{\circ}$ C

的温度区间内,通道均匀性校准精度优于67ps。

三模冗余逻辑负责对分布在 GroupA、GroupB 和 GroupC 中相同测时通道的 3 组冗余测时链路测量值进行判决输出,用以增强系统抗单粒子翻转能力,提高系统可靠性。判决逻辑为首先进行回波入波门判读,去除波门外非合理测时结果。默认输出 GroupA 测时值,GroupB 优先级次之,GroupC 优先级最低。当至少同时有两路合理测时值,才按优先级输出测时值。

## 3.4 TDC 系统设计结果

将设计结果与之前采用 Virtex 4 LX80 的 9 通 道时间测量时间系统的资源使用情况进行了对比,结果如表 1 所示。首先 Virtex 4 方案中并没有在硬件中对延迟链的非线性进行校准,以及相应的减法运算等操作,理论上本设计平均每通道使用资源用量就应高于 Virtex 4 方案资源用量。但由表可以看出,该设计的平均每条通道资源使用量是 Virtex 4 LX80 上资源使用量的一半。另外考虑到 Virtex 4 产品在其结构及性能上均优于 Virtex II,故该设计真正有效地在资源有限器件中实现了优化和改进。

表 1 资源使用对比

Tab.1 Resource usage comparison

| Item         | 9 Channel<br>Triple modular<br>redundancy<br>(V2 V3000) |                | 9 Channel<br>(V4 LX80) |                |                 |

|--------------|---------------------------------------------------------|----------------|------------------------|----------------|-----------------|

| -            | Total<br>usage                                          | Per<br>channel | Total<br>usage         | Per<br>channel | compari-<br>son |

| Flip-flops   | 7 647                                                   | 283.22         | 4 560                  | 506.67         | 55.9%           |

| Lut          | 11 027                                                  | 408.41         | 7 532                  | 836.89         | 48.8%           |

| Block<br>RAM | 27                                                      | 1              | 20                     | 2.22           | 45.1%           |

## 4 TDC 系统性能测试

多通道TDC 系统性能实测通过高精度信号源 Tektronix AFG3022B 同步输出固定时差的信号。其 中一路当作主波信号,另外一路经功分器输出,作为 多路回波信号。

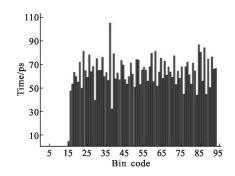

#### 4.1 延迟链非均匀性及校准

以标准的码密度测试方式延迟单元大小, 并用

bin-by-bin 方式校准曲线,图 11、图 12 以 Group A 主波信号通道为例显示了 XC2V3000 内部延迟单元 大小的分布情况及校准曲线。

图 11 延迟单元延迟大小(FPGA Q, Group A, 主波)

Fig.11 Bin width of the delay-line cell (FPGA Q, GroupA,

Main wave)

由图 11 可知,该延迟链上各点延迟情况都比较均匀,但最高时能达到 100 ps,最低是只有 30 ps,故采用bin-by-bin 方式校准非常必要,其结果如图 12 所示。

图 12 延迟链校正曲线(FPGA Q, Group A, 主波)

Fig.12 Calibration curve of the delay-line unit (FPGA Q, GroupA, Main wave)

#### 4.2 测时精度测试

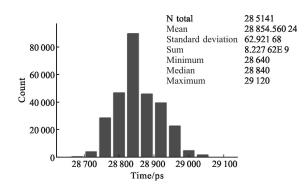

随机挑选其中某一通道信号。该情况下信号源给出 29 ns 的延迟。经 TDC 测量,均值为 28.85 ns,标准差为 62.9 ps,如图 13 所示。SongJian 论文中采用平均延迟的方案进行校准,时间测量结果标准差为 93.1 ps<sup>[10]</sup>。值得注意的是这里两种校准方式不同,该系统采用的是 bin-by-bin 方式,一次测量最大的偏差小于一个最大延迟单元,而平均延迟方式可能会带来较大的积分非线性误差,Song Jian 论文中得到的一个典型的积分非线性误差范围为 (-2.003,+1.855)个延迟单元<sup>[10]</sup>。对比易见,bin-by-bin 校准方式是一种较为合理的校准方式。

图 13 时间测量精度(FPGA Q,Group A,通道 5)

Fig.13 Time measurement accuracy of TDC (FPGA Q, Group A, Channel 5)

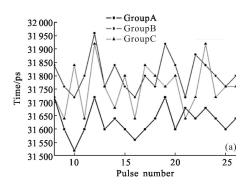

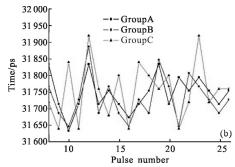

#### 4.3 三模测时一致性测试

该方案为确保数据准确,设计三模方案,对3个测量结果进行判选。故需要对3个测量结果性能的一致性进行比较。

图 14(a)为通道 1 在三模情况下分别测量得到的数据,因为 FPGA 内部走线延迟固有的变化,理应 3 组数据存在 1 个固定的差别,这和图 14(a)中所示一致。通过校准参数,消除走线上的固有延迟差,得到如图 14(b)所示曲线,由图 14(b)可以直观地看见,通道 1 在 GroupC 的测时结果稍差一些。

图 14 FPGA Q 上通道 1 在 GroupA、GroupB、GroupC 里的测时结果 Fig.14 Time measurement results of FPGA Q, Channel 1 in GroupA、GroupB、GroupC

另外由图 14 可见,在时间信号变动较大时(尤其是第 11 个脉冲的数据到第 13 个脉冲的数据),三组的变化趋势一致。而变动校小时变化趋势并不大,这是由延迟单元大小决定的。另外 3 个通道信号变化的一致性表明,图 13 中标准差 62.9 ps 的来源其中相当大一部分是来自于信号源,信号源延迟差的波动导致了上图三通道结果的波动一致性,真实TDC 性能将优于标准差 62.9 ps。

#### 4.4 16 通道静态测距误差表

整机系统需要对 16 个通道的测时性能评估。如表 2 为 16 个通道均取 GroupB 的数据的测时结果。 表中前 8 通道为 FPGA I 上测时结果,后 8 通道为 FPGA Q 上测时结果。

表 2 16 通道测时精度

Tab.2 Time measurement accuracy of the 16-channel TDC

| Channel | Timing accuracy (RMS)/ps | Ranging accuracy (RMS)/cm |  |

|---------|--------------------------|---------------------------|--|

| CH1     | 64                       | 0.96                      |  |

| CH2     | 66                       | 0.99                      |  |

| СНЗ     | 63                       | 0.945                     |  |

| CH4     | 69                       | 1.035                     |  |

| CH5     | 71                       | 1.065                     |  |

| CH6     | 67                       | 1.005                     |  |

| CH7     | 66                       | 0.99                      |  |

| CH8     | 67                       | 1.005                     |  |

| CH9     | 69                       | 1.035                     |  |

| CH10    | 67                       | 1.005                     |  |

| CH11    | 65                       | 0.975                     |  |

| CH12    | 63                       | 0.945                     |  |

| CH13    | 62                       | 0.93                      |  |

| CH14    | 63                       | 0.945                     |  |

| CH15    | 65                       | 0.975                     |  |

| CH16    | 72                       | 1.08                      |  |

## 5 结 论

针对多通道快速激光三维成像雷达的抗辐照、多通道、高集成化、轻量化等要求,该系统实现了一种 16 通道基于资源有限 FPGA 的三通道冗余架构 TDC 系统,完成了密集通道资源优化、多通道均匀校正、译码单元时序优化等设计改进,最终经试验验证,系统测时精度为 62.9 ps,应用于雷达多通道测量

系统后,TDC 系统体积压缩为单块电路板,静态测时精度明显提升。在实际工程中,该系统已经得到了应用。该技术方案不但能够满足激光雷达需求,作为一种抗辐照增强型多通道 TDC 技术,还可应用于诸如卫星导航定位、星载量子通信、星载空间粒子探测等多种空间应用领域。特别是未来将该技术移植到延时链和逻辑资源更为丰富的 FPGA 平台上,测时精度就有可能提进一步提升至 30ps 量级,将拥有更广泛的应用前景。

#### 参考文献:

- [1] Kalisz J, Szplet R, Pasierbinski J, et al. Field-programmable-gate-array-based time-to-digital converter with 200 -ps resolution [J]. *Instrumentation and Measurement*, *IEEE Transactions on*, 1997, 46(1): 51-5.

- [2] Andaloussi M S, Boukadoum M, Aboulhamid E-M. A novel time-to-digital converter with 150 ps time resolution and 2.5 ns pulse-pair resolution; proceedings of the Microelectronics [C]//The 14th International Conference on 2002–ICM, IEEE, 2002.

- [3] Xie D, Zhang Q, Qi G, et al. Cascading delay line time-to-digital converter with 75 ps resolution and a reduced number of delay cells [J]. Review of Scientific Instruments, 2005, 76(1): 014701-3.

- [4] Song Jian. Research of FPGA based precision time-digital conversion circuit [D]. Hefei:University of Science and Technology of China, 2006. (in Chinese) 宋健. 基于 FPGA 的精密时间—数字转换电路研究[D]. 合肥:中国科技大学, 2006.

- [5] Daigneault M, David J P. A novel 10 ps resolution TDC architecture implemented in a 130nm process FPGA; proceedings of the NEWCAS Conference (NEWCAS) [C]// 2010 8th IEEE International, 2010.

- [6] Wang Jinhong, Liu Shubin, Zhao Lei, et al. The 10-ps multitime measurements averaging TDC implemented in an FPGA[J]. Nuclear Science, IEEE Transactions on, 2011, 58 (4): 2011-8.

- [7] Yao Pingping, Zhao Xin, Zhang Yi, et al. Measurement of flight time for satellite laser altimeter based on FPGA [J]. Infrared and Laser Engineering, 2008, 37(4): 679-682. (in Chinese)

- 姚萍萍, 赵欣, 张毅, 等. 基于 FPGA 的星载激光测高仪飞行时间测量[J]. 红外与激光工程, 2008, 37(4): 679-682.

- [8] Qin Xi, The research on the readout electronics for the lon detectors of space plasma exploration [D]. Hefei: University of Science & Technology China, 2013. (in Chinese) 秦熙. 空间等离子体探测中粒子谱仪读出电子学方法的研究[D]. 合肥: 中国科学技术大学, 2013.

- [9] Wu Jinyuan. Several key issues on implementing delay line based TDCs using FPGAs [J]. Nuclear Science, IEEE Transactions on, 2010, 57(3): 1543–1548.

- [10] Song Jian, An Qi, Liu Shubin. A high-resolution time-to-digital converter implemented in field-programmable-gate-arrays [J]. *Nuclear Science*, *IEEE Transactions on*, 2006, 53(1): 236–241.

- [11] Wu Jinyuan, Shi Zonghan. The 10-ps wave union TDC: Improving FPGA TDC resolution beyond its cell delay [C]// proceedings of the Nuclear Science Symposium Conference Record, NSS '08 IEEE, 2008, 10: 19-25.

- [12] Hou Libing, Guo Ying, Huang Genghua, et al. A time-to-digital converter used in photon-counting LIDAR[J]. *Journal of Infrared and Millimeter Waves*, 2012, 31(3): 243. (in Chinese)

侯利冰,郭颖,黄庚华,等.光子计数激光雷达时间-数字

- [13] Wu Jinyuan, Shi Zonghan, Wang I Yrena. Firmware-only implementation of time-to-digital converter (TDC) in fieldprogrammable gate array (FPGA) [C]//Proceedings of the nuclear science symposium conference record, IEEE, 2003.

转换系统[J]. 红外与毫米波学报, 2012, 31(3): 243.

- [14] Liu Shubin, Guo Jianhua, Zhang Yanli, et al. The test of data driven TDC application in high energy physics experiment[J]. *Nuclear Techniques*, 2006, 29(1): 72–76. (in Chinese)

- 刘树彬, 郭建华, 张艳丽, 等. 高精度数据驱动型 TDC 在高能物理实验中应用的研究[J]. 核技术, 2006, 29(1): 72-76.