-

碲镉汞(Hg1−xCdxTe, MCT)材料由于宽光谱内连续带隙可调、高吸收系数、高载流子迁移率以及长的载流子寿命特性,在红外探测器的发展中起到重要的作用。MCT红外探测器的暗电流会增大器件噪声(包含散粒噪声、热噪声、1/f噪声和光子噪声)以及降低焦平面的动态范围[1]。对于长波探测器工作环境背景辐射高,其背景电流可能大于信号电流。高背景电流以及暗电流会使读出电路中积分电容很快饱和,从而降低其信噪比(Signal-to-Noise Ratio, SNR)和动态范围(Dynamic Range, DR)。通过降低探测器的暗电流可以减小读出电路所需的积分电容,提高红外焦平面中的探测器的灵敏度。对于大规模红外焦平面,很难通过在有限的单元电路面积内增大积分电容来延长积分时间。在读出电路中,可以通过加入背景抑制模块来降低探测器的暗电流以及背景电流,从而起到延长积分时间来提高焦平面的信噪比。背景抑制模块可以通过减小注入电流来延长积分时间,提高信噪比。

背景抑制结构主要有电压−电流转换法、电流存储型的背景抑制结构以及基于DAC的自适应背景抑制结构。电压−电流转换法适用于共模背景信号抑制,背景抑制精度较低[2-4]。电流存储型的背景抑制结构适用于差模背景抑制,对于大的背景电流记忆精度高[5-7]。DAC的自适应背景抑制精度高,通过降低读出电路帧率来实现自适应差模背景抑制[8],且记忆效率低。

在长波红外探测器的暗电流分析的基础上,文中基于电压−电流转换法以及电流存储型的背景抑制结构,通过背景信号放大−缩小原理设计了16元的具有背景抑制功能的长波读出电路。背景抑制结构采用共模背景抑制与差模背景抑制相结合,提高对暗电流以及背景电流抑制的精度。在80 K的低温下对该背景抑制模块进行测试分析。

-

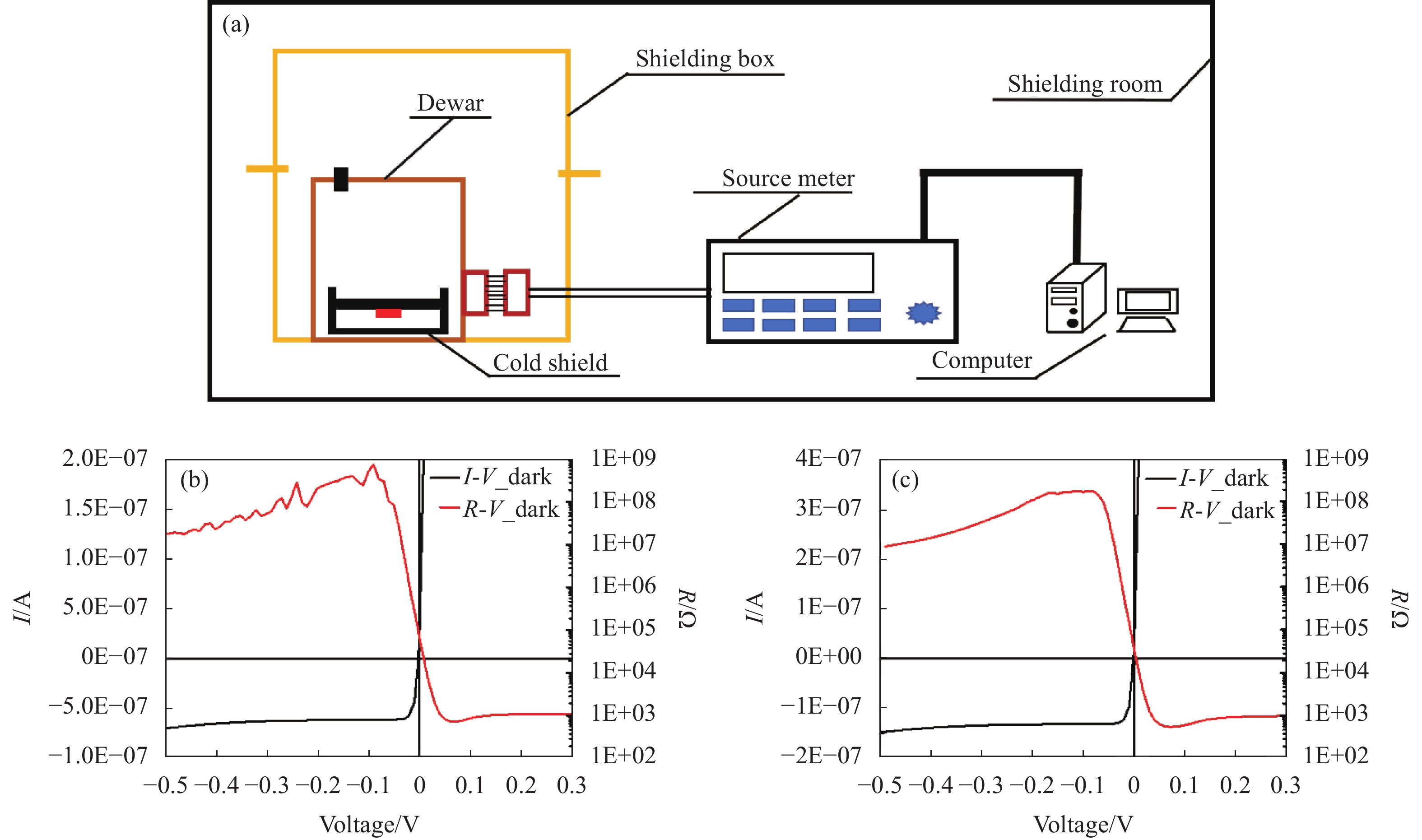

文中首先对8~12 μm的MCT长波红外探测器的暗电流在80 K温度下进行测试分析,以确定读出电路中背景抑制的范围。图1 (a)为I-V测试系统,其中源表采用Keithley 6430,其电流测试精度可以达到fA量级。在测试时,需将器件封装于高真空的杜瓦瓶内,通过液氮实现80 K低温I-V测试。图1 (b)为长波探测器暗电流的I-V以及R-V曲线,在偏压为−50 mV时其暗电流为在61 nA左右,电阻大于100 MΩ。图1 (c)为长波探测器在室温时光电流的I-V以及R-V曲线,未加冷屏,在偏压为−50 mV时其电流在150 nA左右,电阻在100 MΩ,在焦平面测试其值可以作为参考。

由于暗电流的非均匀性会带来较大FPN值,文中对4种MCT长波红外探测器的暗电流在−50 mV偏压下分别取10个进行统计分析,如图2所示。在偏压为−50 mV附近,4种探测器的暗电流方差在1.22~25 nA范围波动,非均匀性在2%~16%范围内,非均匀性平均值在8%左右。探测器的暗电流在70~500 nA范围。基于MCT长波探测器的暗电流水平以及背景电流的考虑,背景抑制水平设定在0~1 μA范围内。

探测器暗电流的非均匀性可以通过差模背景抑制来降低对焦平面性能的影响。基于探测器暗电流的非均匀性,结合读出电路特性分析暗电流非均匀性对64×64长波红外焦平面的影响,如图3所示。当器件的暗电流为100 nA时,暗电流的均方差为8 nA。读出电路的积分电容为2 pF,积分时间为10 μs。在暗背景下只有暗电流进行积分,其积分电压分布如图3(a)所示,电压在0.35~0.65 V范围内波动。当信号电流为500 nA时,从图3(b)可知:由于信号电流和暗电流相差不大,这时暗电流的非均匀性会导致焦平面的FPN值较大,同时积分电压较大容易达到饱和值,积分电压为2.85~3.1 V。通过前面暗电流的测试分析,文中拟设计背景抑制范围为0~1 μA,且能够实现差模背景抑制从而降低暗电流的非均匀性。

-

文中所设计的读出电路单元以及背景抑制模块如图4所示。读出电路单元包含输入级CMI结构、电压−电流转换法背景抑制模块VIBDS以及电流存储型背景抑制模块CMBDS,如图4(a)所示。电流存储型背景抑制结构具有对大的背景电流记忆精度高的特点。背景抑制先通过VIBDS模块实现共模背景抑制,然后将差模背景电流通过输入级CMI结构放大5倍,通过CMBDS模块进行差模背景电流记忆。在信号积分阶段,将CMBDS记忆的差模背景电流通过电流镜缩小5倍再进行差模背景抑制。图4(a)中CM_x0.2为实现电流缩小5倍的电流镜模块,采用共源共栅电流镜结构。图4(a)中积分电容C1为3 pF,采样电容C2为300 fF。

图4(b)为输入级自偏置CMI结构,M1以及M2构成电压−电流转换法背景抑制电路即补偿电流源,实现共模背景信号抑制。补偿电流源采用自级联结构,其输出阻抗的表达式为:

$$ {r}_{{\rm{sel}}}=\sqrt{\frac{2{\mu }_{{\rm{p}}}{C}_{{\rm{ox}}}}{{{I}_{{\rm{sub}}}}^{3}}{W}_{1}{L}_{1}} \cdot \frac{{L}_{2}{N}_{{\rm{ch}}}}{{K}_{1}{K}_{2}} $$ (1) 式中:Isub为补偿电流;K1、K2为MOS管M1、M2的尺寸系数;Nch为沟道掺杂系数。从该公式可知大的沟道长度,可以提高其输出阻抗来增大输出的线性度。自级联结构采用大的宽长比PMOS管可以降低1/f噪声对补偿电流的影响。该补偿电流源结构位于CMI的输入端,通过CMI反馈结构可以提高M2漏极电压的稳定性,从而减小补偿电流的抖动,提高背景抑制的稳定性。VIBDS可以基于探测器暗电流水平,通过其输出特性进行手动粗调。该模块背景抑制后存在欠补偿,再通过CMBDS背景抑制模块进行修正。CMI结构中Output1为电流放大五倍输出端,用于差模背景信号记忆。Output2为电流不做缩放的输出端,用于信号积分。CMI结构简化模型如图4(c)所示,其中e2n_eq为单元噪声的等效输入功率。MOS管的噪声主要为热噪声以及闪烁噪声,其等效电压源可以表示为:

$$ {{e}_{{\rm{n}}}}^{2}=4kT\gamma {g}_{{\rm{m}}}{{R}_{{\rm{D}}}}^{2}+\frac{N}{{C}_{{\rm{ox}}}WLf} $$ (2) 式中:γ、N为工艺相关常数;RD是MOS管的等效负载电阻。因此CMI的等效输入噪声可以表示为[9]:

$$ {{e}^{2}}_{{{\rm{n}}}_{{\rm{eq}}}}={{e}^{2}}_{{{\rm{n}}}_{{\rm{n1}}}}+{{e}^{2}}_{{{\rm{n}}}_{{\rm{n2}}}}+\left(\dfrac{{{g}^{2}}_{{\rm{Mn1}}}}{{{g}^{2}}_{{\rm{Mp1}}}}\right) \cdot ({{e}^{2}}_{{{\rm{n}}}_{{\rm{p1}}}}+{{e}^{2}}_{{{\rm{n}}}_{{\rm{p2}}}}+{{e}^{2}}_{{{\rm{n}}}_{{\rm{p3}}}}+{{e}^{2}}_{{n}_{{\rm{p4}}}}) $$ (3) 式中:e2n_n1~e2n_n2、e2n_p1~e2n_p4分别为图4(c)中相应MOS管的等效噪声电压源;gMn1、gMp1为Mn1以及Mp1的跨导。在单元面积的允许条件下,采用大尺寸的MOS管可以减小噪声的影响。

两步减背景抑制结构在共模背景抑制的基础上再进行差模背景信号抑制,减小由于探测器暗电流非均匀所引起的空间噪声。电流存储型背景抑制结构如图5所示,主要由记忆管Mb,三个记忆电容以及相应的开关构成。该结构的工作原理即在背景电流记忆阶段Ф、Ф1、Ф2、Vb为高电平,其对应的开关处于导通状态。三个环状记忆电容是用于稳定记忆管Mn6的栅压。当其中一个记忆电容受到噪声干扰时其存储的电荷数发生变化,另外两个记忆电容可以起到钳位作用。同时3个环状记忆管可以降低由于开关信号Ф1以及Ф2引起的时钟馈通效应所产生的干扰电压。该干扰电压ΔV1会改变记忆电容中的电荷数量,导致存储的记忆电流产生误差:

$$ \Delta {I}_{{\rm{BDS}}}={g}_{{\rm{m}}}\Delta {V}_{1} $$ (4) 通过3个环状记忆电容可以使得ΔV1降低到原来的CM2/(CM1+CM2),其中CM0=CM1且CM2<CM1[10]。CM2值越小,干扰抑制效果越好。若CM2取值太小,由于寄生电容的影响CM2会明显增大,影响干扰抑制的稳定性。CM2值可以通过后仿所得的寄生参数,对值进行折中调整。在该背景抑制结构中,CM1值为1 pF,CM2为50 fF。因此记忆管的栅压受时钟馈通效应的干扰可以减小到原来的1/20。电流存储型电路受时钟馈通效应以及沟道电荷注入效应的影响。CMOS开关以及虚拟管可以降低该影响。CMOS开关管的时钟溃通引入的误差为:

$$ {\Delta V}_{1}={V}_{{\rm{CLK}}}\left(\frac{{W}_{{\rm{N}}}{C}_{{\rm{ov,N}}}}{{W}_{{\rm{N}}}{C}_{{\rm{ov,N}}}+{C}_{{\rm{s}}}}-\frac{{W}_{{\rm{P}}}{{{C}}}_{{\rm{ov,P}}}}{{W}_{{\rm{P}}}{C}_{{\rm{ov,P}}}+{C}_{{\rm{s}}}}\right) $$ (5) 式中:WN、WP以及Cov,N、Cov,P为NMOS以及PMOS的沟道宽度以及单位交叠电容;Cs为记忆电容。对于CMOS开关,沟道电荷注入所引入的误差可以表示为:

$$ {\Delta V}_{2}=\frac{{C}_{{\rm{ox}}}\left(WL\right) \cdot ({V}_{{\rm{clk}}}+\left|{V}_{{\rm{THP}}}\right|-{V}_{{\rm{THN}}})}{{C}_{{\rm{s}}}} $$ (6) 通过调整CMOS开关的宽长比可以降低时钟馈通效应以及沟道电荷注入效应对记忆管栅压的影响。

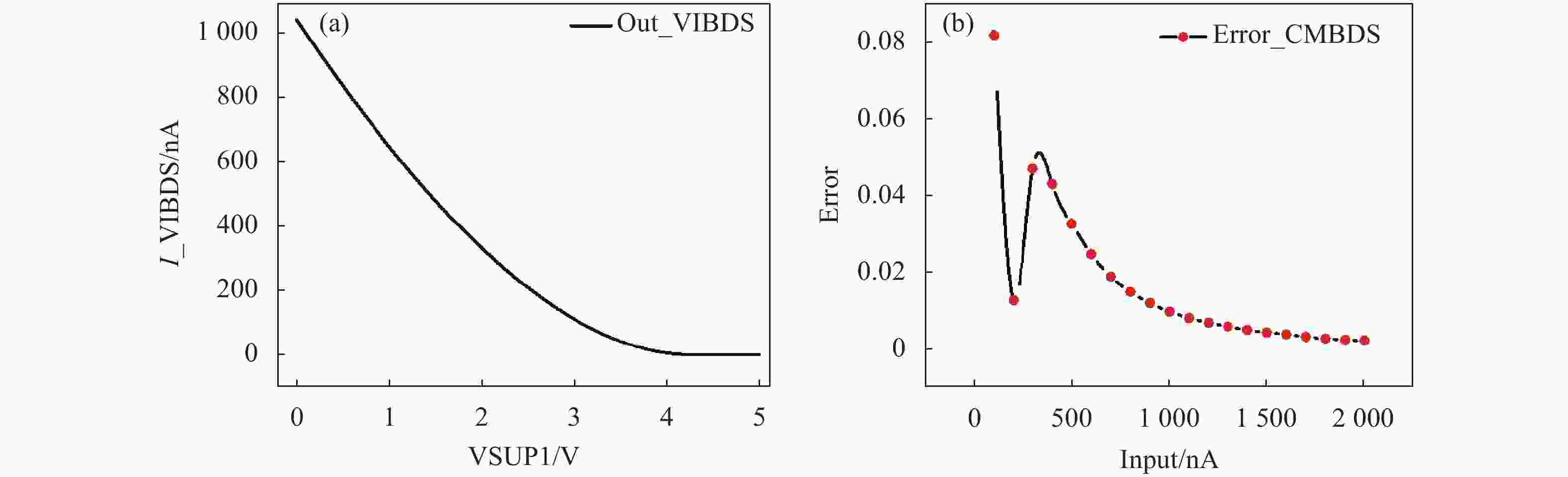

读出电路使用TSMC 0.18 μm 1P6M 5 V工艺。图6为两种背景抑制结构的仿真结果。图6(a)为补偿电流源的输出曲线,其输出范围为0~1 μA。在0~2.5 V,其输出具有良好的线性度,精度可以达到3.35 nA/10 mV。16元具有背景抑制功能的长波读出电路中共用一个补偿电流源的偏置,实现共模背景信号抑制。图6(b)为电流存储型背景抑制精度。当记忆的电流大于0.7 μA时,背景记忆的绝对误差在1%范围内。由于MOS管的输出特性,小偏压下电压稳定性对电流影响较大。CMBDS对于背景电流记忆精度与其记忆电压的稳定性以及记忆电容的漏电流有关,小偏压下记忆电压波动对记忆的电流影响较大。因此通过将差模背景信号放大5倍存储于电流存储型背景抑制电路,然后在读出模式时再将记忆的差模背景电流缩小5倍,可以提高小背景电流的记忆精度从而增大背景抑制精度。

本文所设计的16元线列的读出电路,单个像元面积为100 μm×100 μm,其中差模背景抑制的面积为50 μm×65 μm,共模背景抑制的面积为5 μm×10 μm。由于该读出电路所采用的工艺其电容率较低,因此,单个像元面积较大。通过采用较大的电容率电容工艺可以降低该读出电路的像元尺寸。对于小像元的面阵读出电路,可以通过共享的方式实现该方案。读出电路的整体仿真结果如图7所示,其中图7 (a)为仿真的控制时序,图7(b)为各级输出线性图。仿真中主频时钟为1 MHz,电源电压为5 V,探测器暗电流以及背景电流设置为100 nA,有效光电流选取0.02~1.8 μA。探测器模型选取长波探测器,其结电阻为1 MΩ,结电容为1 pF。Vint为积分电压,Vsamp为采样电压,Vsf为源随输出,Vout为最后buff单位增益缓冲器的输出电压。各级的输出线性度均大于99.9%,输出摆幅为2.1 V。模拟模块的电流约为2.282 mA,数字电流约为2.6125 nA。因此,全电路的功耗约为13.41 mW。

-

芯片采用QFP64封装,如图8(a)所示。将芯片和探测器放置杜瓦内,在低温液氮环境下测试。探测器通过键压的方式与芯片间接互连。探测器的暗电流如图1 (b)所示。电路测试系统如图8(b)所示。采集系统采用NI PXIe-1062Q,其中NI PXI-6552板卡提供时钟信号,NI PXIe-5122板卡采集所需的信号数据。

首先对背景抑制结构进行测试,采用源表Keithley 6430来测试在不同偏压下的电压−电流背景抑制结构的输出特性,如图9(a)、(b)所示。图9(a)为常温下补偿电流的输出曲线,图9(b)为80 K时的补偿电流的输出曲线。常温下补偿电流的输出范围为0~1.1 μA范围内,与仿真结果一致。在0~2 V范围内具有良好线性度,通过拟合其线性度为99.7%。测试温度为80 K时,补偿电流的输出范围为0~2.3 μA。在0~2 V范围内拟合度为99.91%。当背景电流较小即不在补偿电流的线性范围内,通过往小的电流范围进行粗调整,再通过CMBDS模块对其残差的背景电流进行自适应的记忆和抑制。低温下电路的噪声较低且载流子迁移率相对增大,使得其输出范围以及线性度相对于常温下有着较大的提高。

图9(c)、(d)为电流存储型背景抑制的记忆精度测试图,测试温度为80 K。图9(c)为通过Keithley 6430输入电流的方式进行记忆精度的误差分析,以有效信号电流20 nA的积分电压作为参考。记忆20 nA时的背景电流,对40 nA的信号电流进行积分即通过背景抑制有效积分电流为20 nA。当信号电流为60 nA时,其背景电流设置为40 nA,以此类推进行精度测试。从图9(c)可以看出随着记忆的电流增大,背景记忆的精度逐渐提高,与仿真结果一致。差模背景抑制通过背景记忆时信号放大,背景抑制时信号缩小来提高背景抑制精度。当记忆电流大于130 nA时,其记忆的误差小于1%。图9(d)为读出电路与探测器耦合后以温差为15 ℃的响应电压作为参考。记忆温度为20 ℃时的背景电流,对黑体为35 ℃的信号电流进行积分,以此类推。从图9(d)可以看出随着黑体辐射的温度越高,信号电流越大,背景记忆的精度逐渐提高。

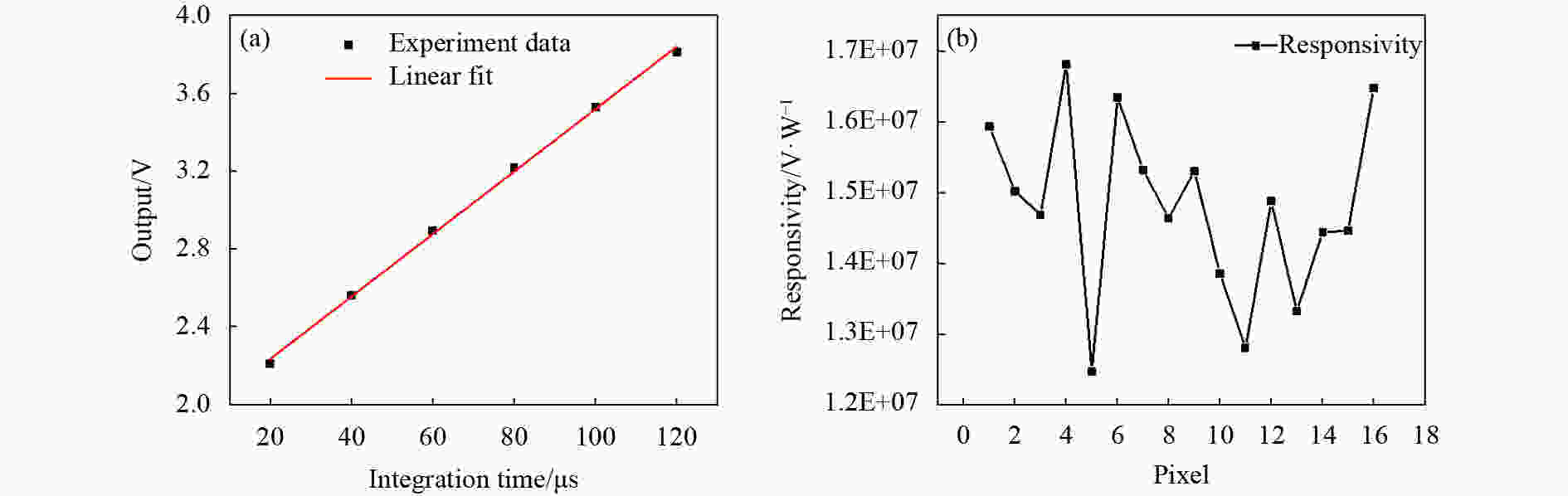

基于国标红外焦平面阵列参数测试方法,对长波红外焦平面进行测试。图10为焦平面的测试结果,首先测试了黑体温度为20 ℃时电路输出信号与积分时间的关系,如图10(a)所示。在输出线性范围内线性度大于99.9%。长波红外焦平面功耗为27.36 mW。开启背景抑制后其功耗约为28 mW,基于其功耗的差值可以计算出单元背景抑制功耗约为40 μW。对于长波红外探测器其暗电流水平在几百纳安范围内,因此,共模背景抑制模块的补偿电流可以设置为1 μA范围内。差模背景抑制功耗较大,主要是由于电流镜放大以及缩小模块导致。在大面阵应用中,通过降低对CMBDS的电流镜放大倍数、采用CMBDS共享模式以及限制VIBDS的输出范围来降低其背景抑制模块的总功耗。图10(b)为焦平面所有像元的响应图,像元平均响应率为1.48×107 V/W,积分间为100 μs。未开启背景抑制时,焦平面FPN值为48.25 mV,RMS噪声为0.597 mV。开启背景抑制后,其FPN值下降为5.8 mV,RMS噪声上升为0.681 mV。读出电路未耦合探测器时,其FPN值为2.08 mV,RMS噪声为0.235 mV。图2(d)为所用长波探测器的暗电流非均匀分布,其均方差为1.227 nA。当积分时间为100 μs时,通过该值计算由暗电流非均匀性所产生的FPN理论值约为40.9 mV。该值与未开启背景抑制时的FPN噪声差7 mV左右。电路具体参数指标如表1所示。通过该表可以看出:开启背景抑制功能后,焦平面的FPN值下降,其RMS噪声以及功耗稍微增大。

表 1 测试性能参数

Table 1. Performance parameters of test

Performance ROIC FPA (BDS off) FPA (BDS on) Supply voltage/V 5 Dynamic range/dB 78.59 70.5 69.35 RMS(noise)/V 2.35×10−4 5.97×10−4 6.81×10−4 Temperature/K 80 Background suppression range/μA 0~2 Memory current error (>130 nA) <1% FPN/V 0.002 0.0482 0.005 Power/mW 27 27.36 28 -

文中基于长波碲镉汞红外探测器暗电流分析的基础上,设计了一种16元的两步背景抑制结构的长波读出电路,通过共模背景抑制以及差模背景抑制有效的降低FPN噪声。背景抑制可以去除信号电流中的背景电流与探测器的暗电流,从而用降低注入电流的方式来延长积分时间,提高红外焦平面的有效动态范围。通过将差模背景信号放大5倍存储于电流存储型背景抑制电路,然后在读出模式时再将记忆的差模背景电流缩小5倍,提高背景抑制精度。通过测试,共模背景抑制范围0~2 μA。当背景电流小于130 nA差模背景记忆精度小于1%。未开启背景抑制时,焦平面FPN值为48.25 mV。开启背景抑制后,其FPN值下降为5.8 mV。基于探测器的暗电流非均匀分布,计算其理论FPN值为40.9 mV。该值与未开启背景抑制时的FPN值差7 mV左右。开启背景抑制功能后,焦平面的FPN值下降,其RMS噪声以及功耗稍微增大。

Long wavelength infrared readout circuit with background suppression function

-

摘要: 为了提高红外焦平面检测目标的灵敏度,目标辐射产生的载流子应尽可能长时间保持,同时应尽可能减少热激发和背景辐射激发的比例。高背景条件下长波红外读出电路的积分电容较快饱和,且长波红外探测器暗电流的非均匀性会影响焦平面的固定图形噪声。基于共模背景抑制结构以及长波碲镉汞探测器暗电流分析的基础上,设计了具有非均匀性矫正的背景抑制电路。传统的背景抑制电路采用单一共模背景抑制或差模背景抑制。差模背景抑制模块的高精度背景记忆一般在小范围区间内。本文背景抑制结构采用共模背景抑制与差模背景抑制相结合,可以在较大的背景噪声范围内有效地降低固定图形噪声以及增大动态范围。该背景抑制结构中共模背景抑制采用电压-电流转换法,差模背景抑制采用电流存储型背景抑制结构。差模背景抑制通过背景记忆时信号放大,背景抑制时信号缩小来提高背景抑制精度。电路采用标准CMOS工艺流片。测试结果表明:读出电路的FPN值为2.08 mV。未开启背景抑制时,焦平面FPN值为48.25 mV。开启背景抑制后,焦平面FPN值降至5.8 mV。基于探测器的暗电流非均匀分布,计算其理论FPN值为40.9 mV。长波红外焦平面输出信号的RMS噪声在0.6 mV左右。Abstract: In order to improve the sensitivity of target detection by IRFPA, the carrier generated by target radiation should be maintained as long as possible. And the proportion of thermal excitation and background radiation excitation should be reduced as much as possible. The integral capacitance of the long-wave infrared (LWIR) readout circuit (ROIC) is easily saturated under high background conditions. And the non-uniformity of the LWIR detector dark current will affect the fixed pattern noise (FPN) of the focal plane array (FPA). Based on the common mode background suppression (BDS) structure and the analysis of dark current for long-wave HgCdTe detector, the BDS circuit with non-uniformity correction was designed. Traditional background suppression circuits only used common mode background suppression or differential mode background suppression. The high-precision background memory of the differential mode background suppression module was generally within a small range. Common mode BDS and differential mode BDS were used for BDS module in this paper, which can effectively reduce the fixed graphics noise and increase the dynamic range in a larger background noise range. For this background suppression circuit, the common mode background suppression used a voltage-current conversion method, and the differential mode background suppression used a current storage type background suppression structure. The background signal was amplified during background memory and signal was reduced during BDS for differential mode BDS. It could improve BDS accuracy. The circuit adopted standard CMOS process tape out. The test result shows that the FPN of ROIC is 2.08 mV. The FPN of the FPA without background suppression is 48.25 mV. When background suppression is turned on, its FPN noise is 5.8 mV. Based on the detector's non-uniform distribution of dark current, the theoretical FPN value is calculated to be 40.9 mV. The RMS noise of the output signal of the long-wave infrared focal plane is about 0.6 mV.

-

Key words:

- background suppression /

- dark current /

- readout circuit /

- LWIR

-

表 1 测试性能参数

Table 1. Performance parameters of test

Performance ROIC FPA (BDS off) FPA (BDS on) Supply voltage/V 5 Dynamic range/dB 78.59 70.5 69.35 RMS(noise)/V 2.35×10−4 5.97×10−4 6.81×10−4 Temperature/K 80 Background suppression range/μA 0~2 Memory current error (>130 nA) <1% FPN/V 0.002 0.0482 0.005 Power/mW 27 27.36 28 -

[1] Burlakov I D, Selyakov A Y, Ponomarenko V P, et al. Noise processes modeling in HgCdTe infrared photodiode detectors[C]//Infrared Technology and Applications XXXVI. International Society for Optics and Photonics, 2010, 7660: 76603A. [2] Xie L, Xia X J, Zhou Y F, et al. Pixel readout circuit with novel background suppression techinque for LWIR applications[C]//2009 Asia Pacific Conference on Postgraduate Research in Microelectronics & Electronics (PrimeAsia). IEEE, 2009: 345-348. [3] Chen X Q, Lv Q. A versatile CMOS readout integrated circuit for microbolometric infrared focal plane arrays [J]. Optik, 2013, 124(20): 4639-4641. [4] Zhou T, Dong T, Su Y, et al. A CMOS readout with high-precision and low-temperature-coefficient background current skimming for infrared focal plane array [J]. IEEE Transactions on Circuits and Systems for Video Technology, 2015, 25(8): 1447-1455. [5] Bodnar R, Redman-White W. High-accuracy current memory in HV CMOS technology [J]. IEEE Transactions on Circuits and Systems Ii-Express Briefs, 2013, 60(6): 321-325. [6] Woo D H, Kang S G, Lee H C. Novel current-mode background suppression for 2-D LWIR applications [J]. IEEE Transactions on Circuits and Systems Ii-Express Briefs, 2005, 52(9): 606-610. [7] Yang G, Sun C, Shaw T, et al. High dynamic range low-noise focal plane readout for VLWIR applications implemented with current mode background subtraction[C]//Infrared Readout Electronics IV. International Society for Optics and Photonics, 1998, 3360: 42-51. [8] Zhou T, Zhao J, He Y, et al. A Readout Integrated Circuit (ROIC) employing self-adaptive background current compensation technique for Infrared Focal Plane Array (IRFPA) [J]. Infrared Physics & Technology, 2018, 90: 122-132. [9] Kulah H, Akin T. A current mirroring integration based readout circuit for high performance infrared FPA applications [J]. IEEE Transactions on Circuits and Systems Ii-Analog and Digital Signal Processing, 2003, 50(4): 181-186. [10] Daubert S J, Vallancourt D, Tsividis Y P. Current copier cells [J]. Electronics Letters, 1988, 24(25): 1560-1562. -

下载:

下载: